## Mixed Logic Understanding

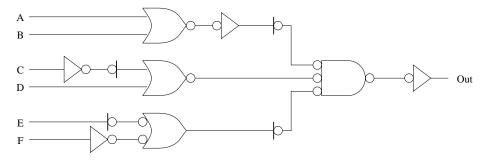

**Part A** You have obtained the following schematics with no description of their operation. Fortunately, the designer used a mixed logic design strategy.

$F_{(A,B,C,D,E,F)} = \underline{\qquad}$

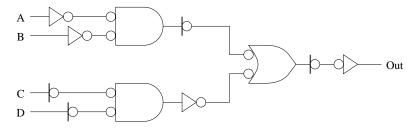

Part B Express the function computed by this circuit.

## $F_{(A,B,C,D)} = \underline{\qquad}$

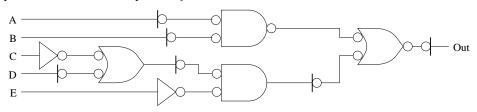

Part C Express the function computed by this circuit.

$F_{(A,B,C,D,E)} = -$

Part D How many transistors are required for the circuit implementation above?

number of transistors = \_\_\_\_\_

**Part E** Now change the implementation to use NAND and NOT gates. Accomplish this only by adding buffers and changing bubble pairs.

Part F How many transistors are required for the new implementation?

number of transistors = \_\_\_\_\_

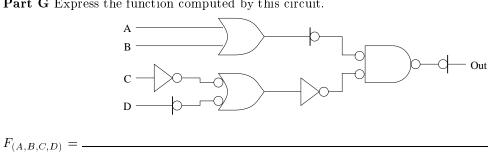

Part G Express the function computed by this circuit.

Part H How many transistors are required for the circuit implementation above?

number of transistors = \_\_\_\_\_

Part I Now change the implementation to use NOR and NOT gates. Accomplish this only by adding buffers and changing bubble pairs.

Part J How many transistors are required for the new implementation?

number of transistors = \_\_\_\_\_

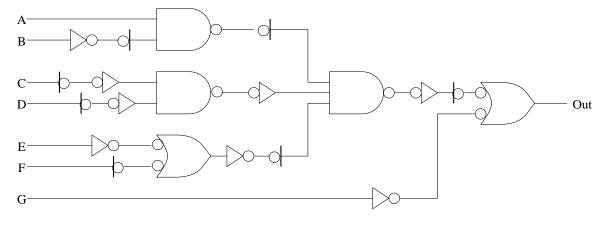

${\bf Part}~{\bf K}$  Express the function computed by this circuit.

$F_{(A,B,C,D,E,F,G)} = \_$

Part L How many transistors are required for the circuit implementation above?

number of transistors = \_\_\_\_\_

**Part M** Now change the implementation to use 2-input and 3-input NOR and NOT gates. Accomplish this only by adding buffers and changing bubble pairs.