ECE2020 Test 2 Summer 2014 GTLName: \_\_\_\_\_\_June 27, 2014Calculators not allowed. Show your work for any possible partial credit or in some cases for<br/>any credit at all. Note the last page shows you some blank K maps just in case you need them<br/>on this exam. 6 pages, possible 100 points.

Problem 1 (20 points) For the bit representations below, determine the most negative value, most positive value, and step size (difference between sequential values). All answers must be expressed in decimal notation just like the practice problems we did in class (using k, M notation). Fractions (for example 3/16ths) must be used. All signed representations are two's complement signed numbers. You must show your work.

| representation       | most negative value | most positive value | step size |

|----------------------|---------------------|---------------------|-----------|

| unsigned integer     |                     |                     |           |

| (15 bits). (0 bits)  |                     |                     |           |

| Signed integer       |                     |                     |           |

| (15 bits). (0 bits)  |                     |                     |           |

| unsigned fixed-point |                     |                     |           |

| (15 bits). (8 bits)  |                     |                     |           |

| signed fixed-point   |                     |                     |           |

| (15 bits). (8 bits)  |                     |                     |           |

Problem 2 Part A Arithmetic (10 points) For each problem below, compute the operations using the rules of arithmetic, and indicate whether an overflow occurs assuming all numbers are expressed using a five bit **unsigned** representation

$$\begin{array}{cccc} 0 & 1 & 0 & 1 & 1 & \\ + & 1 & 1 & 0 & 0 & 1 & \\ \end{array} \\ \begin{array}{c} 0 & 1 & 0 & 1 & 0 & 1 \\ + & 0 & 0 & 1 & 0 & 0 \end{array}$$

result

unsigned error?

Problem 2 Part B Arithmetic (10 points) For each problem below, compute the operations using the rules of arithmetic, and indicate whether an overflow occurs assuming all numbers are expressed using a a five bit **signed** two's complement representations.

| 01011  | $1\ 0\ 1\ 1\ 1$ | 01000         | 10011         |

|--------|-----------------|---------------|---------------|

| +01101 | +01001          | <u>-00101</u> | <u>-00110</u> |

result

| signed<br>error? |  |  |  |

|------------------|--|--|--|

| error?           |  |  |  |

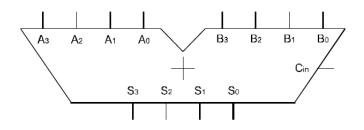

Problem 2 part C Arithmetic (10 points) The adder below adds two four bit numbers X and Y and produces a four bit result S. Add the digital logic to support subtraction as well as addition. Label inputs  $X_3$ ,  $X_2$ ,  $X_1$ ,  $X_0$ ,  $Y_3$ ,  $Y_2$ ,  $Y_1$ ,  $Y_0$ , as well as outputs  $Z_3$ ,  $Z_2$ ,  $Z_1$ ,  $Z_0$ . Do not put in the circuitry to determine errors.

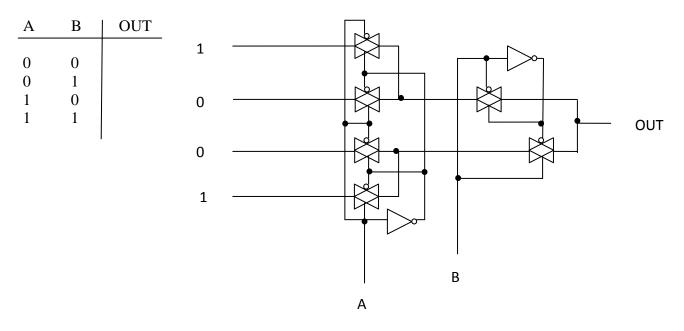

3) (10 points) Complete the truth table for the following logic block.

What boolen function (if any) does the circuit implement?

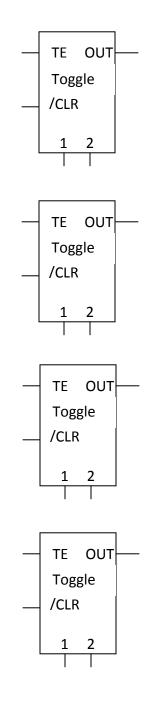

4) Counters (10 points) Connect the toggle cells below to build a divide by 11 counter. Be sure to include an external Count Enable and an external active high clear. Include any circuitry needed to allow this to work in multiple digit counters (like in an alarm clock). You do not have to used mixed logic.

5) (15 points) Consider the following circuit. For each combination of inputs listed below, determine the corresponding outputs. You must show your work and reasoning for any credit. Do not just put an answer without explaining.

|   |   |                 |                   |                  |   |                                        |                               |                  | - |  |

|---|---|-----------------|-------------------|------------------|---|----------------------------------------|-------------------------------|------------------|---|--|

| A |   | In <sub>0</sub> | 2 to 4            | Out <sub>0</sub> |   | In <sub>0</sub>                        | 4 to 2                        | Out <sub>0</sub> |   |  |

| В |   | In <sub>1</sub> | 2 to 4<br>Decoder | Out <sub>2</sub> |   | <br>In <sub>1</sub><br>In <sub>2</sub> | 4 to 2<br>Priority<br>Encoder | Out <sub>1</sub> |   |  |

| С |   | — En            |                   | Out <sub>3</sub> |   | In <sub>3</sub>                        | ln2 > ln1                     | V<br>>In0 >in3   |   |  |

| А | В | С               | D                 | E                | F |                                        |                               |                  |   |  |

| 0 | 0 | 0               |                   |                  |   |                                        |                               |                  |   |  |

| 0 | 0 | 1               |                   |                  |   |                                        |                               |                  |   |  |

| 0 | 1 | 0               |                   |                  |   |                                        |                               |                  |   |  |

| 0 | 1 | 1               |                   |                  |   |                                        |                               |                  |   |  |

| 1 | 0 | 0               |                   |                  |   |                                        |                               |                  |   |  |

| 1 | 0 | 1               |                   |                  |   |                                        |                               |                  |   |  |

| 1 | 1 | 0               |                   |                  |   |                                        |                               |                  |   |  |

|   | 1 | 1               | 1                 |                  |   |                                        |                               |                  |   |  |

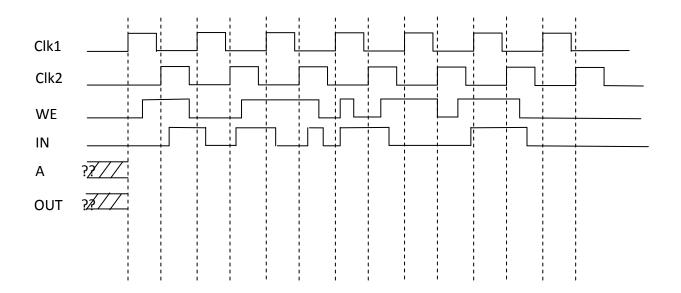

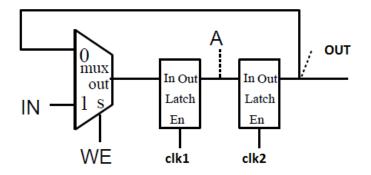

6) Registers (15 points) Consider the register implementation below.

Assume the following signals are applied to the register above. Draw the signal at point A (output of the first latch), the signal at point OUT (output of second latch). Assume A and OUT start at unknown values which are shown below as both a high and a low at the same time with cross hatches drawn between the two values.