ECE 2020-C 4 Problems, 8 pages

## Fundamentals of Digital Design Exam Three

This exam will be conducted according to the Georgia Tech Honor Code. I pledge to neither give nor receive unauthorized assistance on this exam and to abide by all provisions of the Honor Code.

| Signed (With your Full Legal Name):                                                                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                  |

| Instructions: Instructions: This is a closed book, closed note exam. Calculators are not permitted. If you have a question, raise your hand and I will come to you. Please work the exam in pencil and do not separate the pages |

| of the exam. For maximum credit, show your work.                                                                                                                                                                                 |

| Good Luck!                                                                                                                                                                                                                       |

| Your Name (please print):                                                                                                                                                                                                        |

| For maximum (and partial) credit, show your work.                                                                                                                                                                                |

| Good Luck!                                                                                                                                                                                                                       |

18

30

20

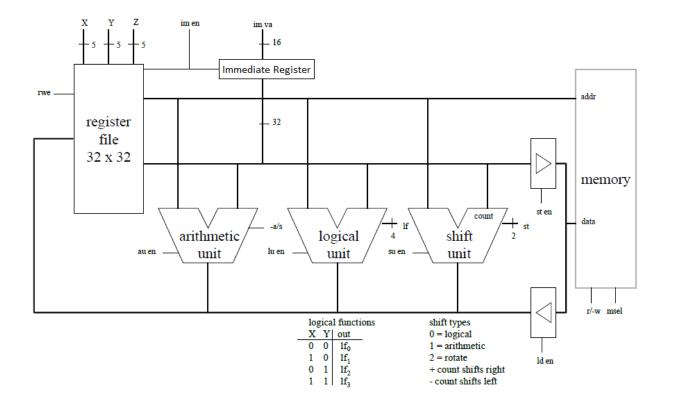

## **Datapath Signals and Diagram**

| Cycle | Cycle number                |

|-------|-----------------------------|

| X     | Register driven onto X bus  |

| Y     | Register driven onto Y bus  |

| Z     | Register written from Z bus |

| rwe   | Register write enable       |

| im_en | Immediate enable on Y bus   |

| im_va | Immediate value             |

| au_en | Arithmetic unit enable      |

| ā/s   | Register driven onto X bus  |

| lu_en           | Logical unit enable                |

|-----------------|------------------------------------|

| lf              | Logical function                   |

| su_en           | Shift unit enable                  |

| st              | Shift type                         |

| ld_en           | Load enable                        |

| st_en           | Store enable                       |

| r/ <del>w</del> | Read/write $(0 = write, 1 = read)$ |

| msel            | Memory select                      |

| description     | Operation description              |

Problem 1 (4 parts, 12 points)

**Fundamentals**

Part A (4 points) Suppose the following inputs (in hexadecimal, denoted by 0x) are applied to an 8-bit shifter. Determine the output (in hexadecimal).

| Shift Type | Shift Amount | Input Value | Output Value |

|------------|--------------|-------------|--------------|

| arithmetic | 0xFE         | 0x52        |              |

| rotate     | 0x05         | 0x14        |              |

Part B (2 points) Flip/flops are different from latches in that the output changes constantly if the control signal is asserted.

- a) True

- b) False

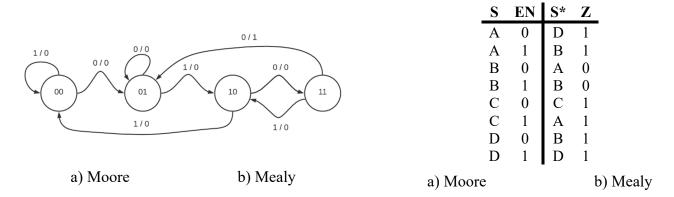

Part C (4 points) Identify whether the following systems are Moore or Mealy machines.

Part D (2 points) Which of the following functional units is a sequential element that controls the timing for the overall datapath?

- a) Logic Unit

- b) X Bus

- c) Register File

- d) Memory Select signal

Problem 2 (2 parts, 18 points)

Latches and Flip/Flops

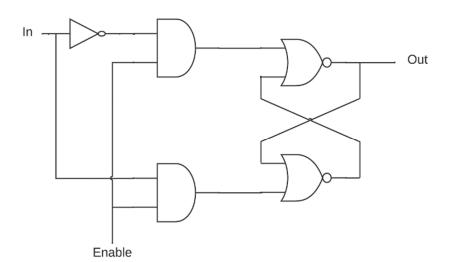

Part A (8 points) For the circuit below, complete the truth table describing its behavior.

| In | Enable | Out |

|----|--------|-----|

| 0  | 0      |     |

| 0  | 1      |     |

| 1  | 0      |     |

| 1  | 1      |     |

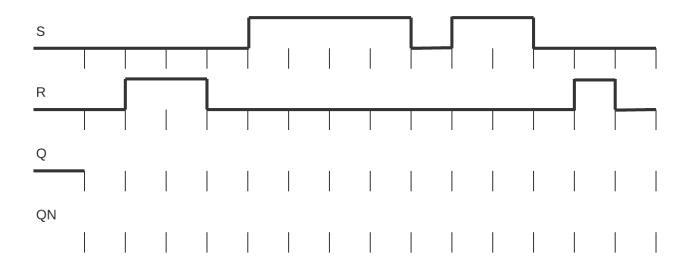

PART B (10 points) Predict the expected output (Q and QN) for an SR latch given the input waveforms shown below. Assume that there is a 10 ns delay for each gate and that the time scale is 10 ns per division. Assume that the latch is initially stable in the Reset state.

Problem 3 (3 parts, 30 points)

Finite State Machines

Consider the following excitation table for a finite state machine with X as the input and Y as the output.

| Q2 | Q1 | X | <b>Q2</b> * | Q1* | Y |

|----|----|---|-------------|-----|---|

| 0  | 0  | 0 | 0           | 1   | 0 |

| 0  | 0  | 1 | 1           | 1   | 0 |

| 0  | 1  | 0 | 1           | 0   | 1 |

| 0  | 1  | 1 | 0           | 0   | 1 |

| 1  | 0  | 0 | 1           | 1   | 0 |

| 1  | 0  | 1 | 0           | 1   | 0 |

| 1  | 1  | 0 | 0           | 0   | 1 |

| 1  | 1  | 1 | 1           | 0   | 1 |

PART A (10 points) Draw its finite state machine diagram using the circles below. Label all states, inputs, and outputs.

Consider the following excitation table for a finite state machine with X as the input and Y as the output.

| Q2 | Q1 | X | <b>Q2</b> * | Q1* | Y |

|----|----|---|-------------|-----|---|

| 0  | 0  | 0 | 0           | 1   | 0 |

| 0  | 0  | 1 | 1           | 1   | 0 |

| 0  | 1  | 0 | 1           | 0   | 1 |

| 0  | 1  | 1 | 0           | 0   | 1 |

| 1  | 0  | 0 | 1           | 1   | 0 |

| 1  | 0  | 1 | 0           | 1   | 0 |

| 1  | 1  | 0 | 0           | 0   | 1 |

| 1  | 1  | 1 | 1           | 0   | 1 |

PART B (10 points) Derive the simplified excitation and output equations needed to build the sequential circuit diagram for this finite state machine.

Y = \_\_\_\_

PART E (10 points) Draw the sequential circuit diagram for the state machine using the building blocks below and any basic gates (AND, OR, NAND, NOR, XOR, NOT) you require. Assume clock inputs to the flip/flops (and any other control signals) are already connected.

Spring 2022 18 April 2022

Problem 4 (2 parts, 20 points)

Finite State Machines

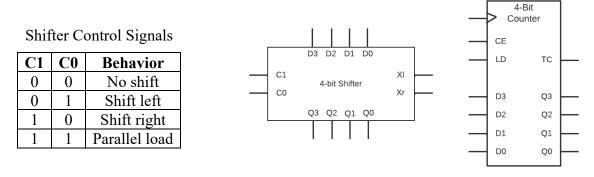

Consider the following sequential building blocks.

PART A (10 points) Design an 8-bit rotate register (without carry) using the 4-bit bidirectional shifters above.

PART B (10 points) Design a binary counter that counts from 15 to 37 using the 4-bit counter with parallel load above. Assume that the counter begins operation based on the load signal.

ECE 2020-C 4 Problems, 8 pages

## Fundamentals of Digital Design Exam Three

Spring 2022 18 April 2022

Problem 5 (3 parts, 20 points)

Microcode

Using the datapath on Page 2, write microcode fragments for the following procedures. Express all values in hexadecimal notation. Use 'x' when a value does not matter. For maximum credit, complete the description field to describe the sub-operation for each row. In each part, modify only registers 3 and 6.

$$R_3 = (R_6 \text{ or } R_1) \text{ and } R_2$$

| # | X | Y | Z | rwe | im | im | au | a/s | lu | LF | su | ST | st | ld | r/w | msel | Description |

|---|---|---|---|-----|----|----|----|-----|----|----|----|----|----|----|-----|------|-------------|

|   |   |   |   |     | en | va | en |     | en |    | en |    | en | en |     |      |             |

| 1 |   |   |   |     |    |    |    |     |    |    |    |    |    |    |     |      |             |

| 2 |   |   |   |     |    |    |    |     |    |    |    |    |    |    |     |      |             |

| 3 |   |   |   |     |    |    |    |     |    |    |    |    |    |    |     |      |             |

$$R_3 = \frac{R_4}{4} + R_7$$

| # | X | Y | Z | rwe | im | im | au | a/s | lu | LF | su | ST | st | ld | r/w | msel | Description |

|---|---|---|---|-----|----|----|----|-----|----|----|----|----|----|----|-----|------|-------------|

|   |   |   |   |     | en | va | en |     | en |    | en |    | en | en |     |      |             |

| 1 |   |   |   |     |    |    |    |     |    |    |    |    |    |    |     |      |             |

| 2 |   |   |   |     |    |    |    |     |    |    |    |    |    |    |     |      |             |

| 3 |   |   |   |     |    |    |    |     |    |    |    |    |    |    |     |      |             |

| 4 |   |   |   |     |    |    |    |     |    |    |    |    |    |    |     |      |             |

$$M[R_6] = (R_4 + R_3) - 7$$

| # | X | Y | Z | rwe | im | im | au | a/s | lu | LF | su | ST | st | ld | r/w | msel | Description |

|---|---|---|---|-----|----|----|----|-----|----|----|----|----|----|----|-----|------|-------------|

|   |   |   |   |     | en | va | en |     | en |    | en |    | en | en |     |      |             |

| 1 |   |   |   |     |    |    |    |     |    |    |    |    |    |    |     |      |             |

| 2 |   |   |   |     |    |    |    |     |    |    |    |    |    |    |     |      |             |

| 3 |   |   |   |     |    |    |    |     |    |    |    |    |    |    |     |      |             |

| 4 |   |   |   |     |    |    |    |     |    |    |    |    |    |    |     |      |             |