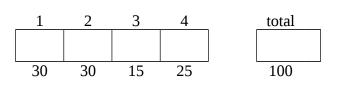

| ECE 2020C           | Fundamentals of Digital Design | Spring 2019  |

|---------------------|--------------------------------|--------------|

| 4 problems, 5 pages | Exam Three                     | 4 April 2019 |

|                     |                                |              |

*Instructions:* This is a closed book, closed note exam. Calculators are not permitted. If you have a question, raise your hand and I will come to you. Please work the exam in pencil and do not separate the pages of the exam. For maximum credit, show your work. *Good Luck!*

Your Name (*please print*) \_\_\_\_\_\_

| ECE 2020C                     | Fundamentals of Digital Design                                                                                                                                                         | Spring 2019                                                |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| 4 problems, 5 pages           | Exam Three                                                                                                                                                                             | 4 April 2019                                               |

| Problem 1 (3 parts, 30 points | )                                                                                                                                                                                      | Memory Chips/Systems                                       |

| words. Assume both the DRA    | <b>512 MByte</b> DRAM chip organized as <b>12</b> M cell and the DRAM chip are square. Ty address. Using the organization approach hip. <i>Express all answers in decimal (not pow</i> | he column number and offset discussed in class, answer the |

| total number of bits in       | address                                                                                                                                                                                |                                                            |

| number of colum               | ns                                                                                                                                                                                     |                                                            |

| column decoder required       | d ( <i>n</i> to <i>m</i> )                                                                                                                                                             |                                                            |

| number of words per o         | column                                                                                                                                                                                 |                                                            |

| type of mux required (        | ( <i>n</i> to <i>m</i> )                                                                                                                                                               |                                                            |

| number of address lines in c  | olumn offset                                                                                                                                                                           |                                                            |

|                               | <b>128 MByte</b> memory system with <b>8 millio</b><br><b>bit word</b> memory DRAM chip.                                                                                               | n addresses of 16 <u>byte</u> words                        |

| word address lines for memo   | ry system                                                                                                                                                                              |                                                            |

| chips needed in one ba        | ink                                                                                                                                                                                    |                                                            |

| banks for memory syst         | em                                                                                                                                                                                     |                                                            |

| memory decoder required (     | (n to m)                                                                                                                                                                               |                                                            |

**Part C** (8 points) Design a **512K address by 4** <u>byte</u> memory system with **512K** address by **8-bit** memory chips. *Label all busses and indicate bit width*. Assume R/W is connected and not shown here. Use a bank decoder if necessary. Be sure to include the address bus, data bus, and MSEL.

DRAM chips required

| ECE 2020C           | Fundamentals of Digital Design | Spring 2019  |

|---------------------|--------------------------------|--------------|

| 4 problems, 5 pages | Exam Three                     | 4 April 2019 |

# Problem 2 (3 parts, 30 points)

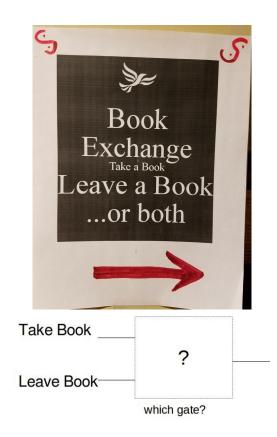

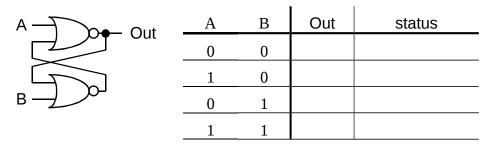

**Part A** (12 points) For the circuit below, complete the truth table describing its behavior. Then label the status of each row from the following choices: SET, RESET, HOLD, DISALLOWED.

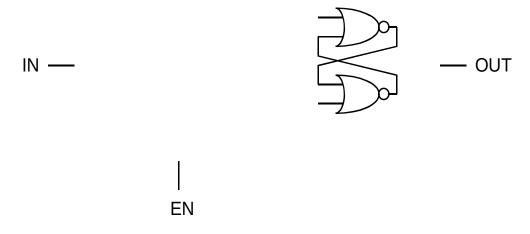

**Part B** (9 points) Now implement a transparent latch using this circuit plus additional basic gates (AND, OR, NAND, NOR, and NOT). Label inputs IN and EN. Label output OUT. Do **not** attempt to employ mixed logic notation.

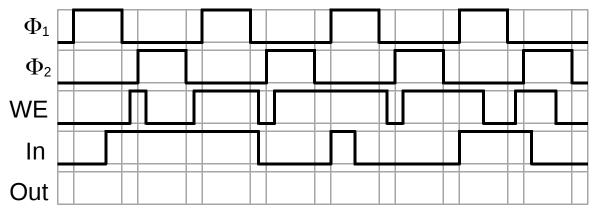

**Part C** (9 points) Assume the following signals are applied to a register with write enable. Draw the output signal **Out**. Draw a vertical line where **In** is sampled. Assume **Out** starts at zero.

Latches

| ECE 2020C           | Fundamentals of Digital Design | Spring 2019  |

|---------------------|--------------------------------|--------------|

| 4 problems, 5 pages | Exam Three                     | 4 April 2019 |

|                     |                                |              |

**Counter Design**

## Problem 3 (2 parts, 15 points)

**Part A** (7 points) Design a toggle cell using *only* transparent latches, inverters, and 2-to-1 multiplexers (*no basic gates besides inverters*). Use icons for the latches and muxes. Your toggle cell should have an active high toggle enable input **TE**, and an active low clear input  $\overline{\text{Clear}}$ , two-phase non-overlapping clock inputs  $\Phi_1$  and  $\Phi_2$ , and a single output **Out**. The  $\overline{\text{Clear}}$  signal has precedence over **TE**. *Label all signals*.

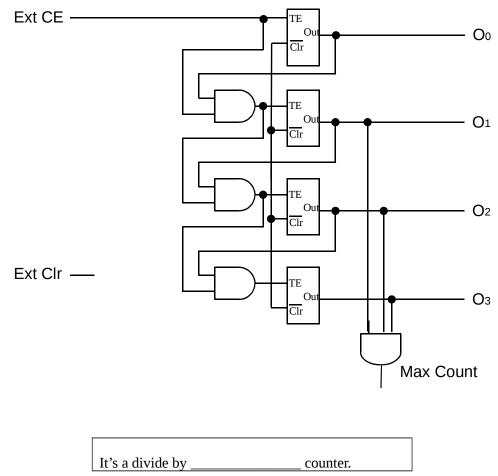

**Part B** (8 points) Consider the following incomplete counter. Based on the completed Max Count detector, determine and describe the counter type. Then complete the counter by properly generating the active low Clr signal when either the external clear is asserted or the counter is about to exceed the maximum count. Use any basic gates required.

| C0; C1 C0 / 11<br>15 cents<br>C1 C0 / C1 /<br>C1 C0 / C1 /<br>C1 C0 / C1 /<br>10 cents<br>C1 / | 01<br>5 cents<br>C0 / |

|------------------------------------------------------------------------------------------------|-----------------------|

| <b>Part A</b> (5 points) Determine the minimum cost of a bag of pret                           | tzels.                |

### Problem 4 (3 parts, 25 points)

4 problems, 5 pages

A state diagram for the controller of the StickyFinger snack machine is shown below. The machine accepts nickels, dimes, and quarters, and does not give change. It sometimes dispenses a bag of pretzels when coins are inserted. Slugs are not detected. The inputs to the controller are C1 and C0, which indicate which coin is inserted according to the following table.

Fundamentals of Digital Design

Exam Three

| 0             |    | 0         |

|---------------|----|-----------|

| coin inserted | C1 | <b>C0</b> |

| nickel        | 0  | 1         |

| dime          | 1  | 0         |

| quarter       | 1  | 1         |

|               | ~  |           |

When the P output signal is asserted, a snack bag of pretzels is dispensed. The states keep track of how much money the machine "believes" you have inserted so far. They are number 00 for zero cents, 01 for five cents, 10 for ten cents, 11 for fifteen cents. Unfortunately, as you can see from the state diagram, the machine is not always accurate in keeping track of the money you have inserted.

C1 C0 / P

C0 /

cents.

cents.

C1/

00

0 cents

Pretzels cost a minimum of \_\_\_\_\_

Fill in as many coins as you need for your example:

C1 / P

How much money would you lose in this example?

| <b>Part C</b> (12 points) Fill in the state table corresponding to this state machine. |    |    |    |     |     |   |   |    |    |    |    |     |     |   |  |

|----------------------------------------------------------------------------------------|----|----|----|-----|-----|---|---|----|----|----|----|-----|-----|---|--|

| S1                                                                                     | S0 | C1 | C0 | NS1 | NS0 | Р | _ | S1 | S0 | C1 | C0 | NS1 | NS0 | Р |  |

| 0                                                                                      | 0  | 0  | 1  |     |     |   |   | 1  | 0  | 0  | 1  |     |     |   |  |

| 0                                                                                      | 0  | 1  | 0  |     |     |   |   | 1  | 0  | 1  | 0  |     |     |   |  |

| 0                                                                                      | 0  | 1  | 1  |     |     |   |   | 1  | 0  | 1  | 1  |     |     |   |  |

| 0                                                                                      | 1  | 0  | 1  |     |     |   |   | 1  | 1  | 0  | 1  |     |     |   |  |

| 0                                                                                      | 1  | 1  | 0  |     |     |   |   | 1  | 1  | 1  | 0  |     |     |   |  |

| 0                                                                                      | 1  | 1  | 1  |     |     |   |   | 1  | 1  | 1  | 1  |     |     |   |  |

5

| cording to the following table. |    |           |  |  |

|---------------------------------|----|-----------|--|--|

| coin inserted                   | C1 | <b>C0</b> |  |  |

| nickel                          | 0  | 1         |  |  |

| dime                            | 1  | 0         |  |  |

| quarter                         | 1  | 1         |  |  |

| ECE 2020C |  |

|-----------|--|

|           |  |

**State Machines**

Spring 2019