5 February 2019

| Your Name ( <i>please print</i> ) |  |

|-----------------------------------|--|

|-----------------------------------|--|

This exam will be conducted according to the Georgia Tech Honor Code. I pledge to neither give nor receive unauthorized assistance on this exam and to abide by all provisions of the Honor Code.

Signed \_\_\_\_\_

${\it Instructions:}\ {\it This is a closed book, closed note exam. Calculators are not permitted.}$

If you have a question, raise your hand and I will come to you; do not leave your seat.

Please work the exam in pencil and do not separate the pages of the exam.

For maximum credit, show your work.

Good Luck!

|   | 1  | 2  | 3  | 4  |

|---|----|----|----|----|

|   |    |    |    |    |

| L |    |    |    |    |

|   | 30 | 20 | 30 | 20 |

Problem 1 (3 parts, 30 points)

Part A (12 points) For the expression below, create a switch level implementation using N and P type switches. Assume both inputs and their complements are available. Your design should contain no shorts or floats. Use as few transistors as possible. Switch-level Design

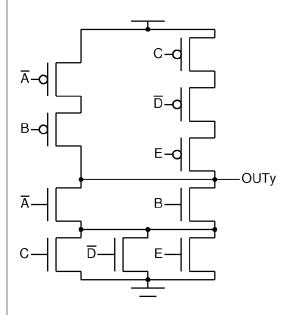

Part B (8 points) Given the circuit shown below right, what expression is  $\overline{OUTy}$ ? (Hint: what does the pull down network implement?)

$$OUTx = (A + \overline{B}) \cdot (\overline{C} + \overline{D}) \cdot E$$

$$\overline{OUTy} =$$

4 problems, 7 pages

Exam One

5 February 2019

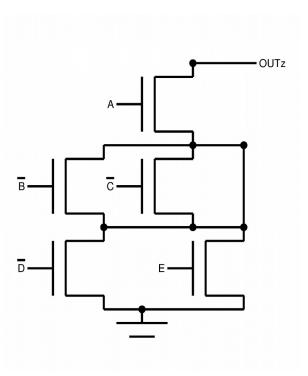

Part C (10 points) Given the pull-down network below, draw the missing pull-up network so that the circuit contains no floats or shorts. Assume both inputs and their complements are available. Also, write the Boolean expression computed by the completed circuit. (The expression should have complements only over the individual input signals, not over subexpressions.)

$Out_Z =$

4 problems, 7 pages

Exam One

5 February 2019

Problem 2 (3 parts, 20 points)

Boolean Algebra

Part A (5 points) Transform the following Boolean expression to a form where it can be implemented using switches (i.e., there should only be bars over input variables, not over operations). The behavior of the expression should remain unchanged. **Do not implement**.

$$Out_A = \overline{X + (\overline{Y + (\overline{Z} + W)}) \cdot (\overline{P} + Q \cdot \overline{S})}$$

$Out_A =$

Part B (6 points) Derive a standard sum of products (using minterms) and a standard product of sums (using maxterms) expression for the truth table below. Every input should be in each minterm or maxterm.

| A | В | C | $F_{(A,B,C)}$ |

|---|---|---|---------------|

| 0 | 0 | 0 | 1             |

| 0 | 0 | 1 | 0             |

| 0 | 1 | 0 | 1             |

| 0 | 1 | 1 | 1             |

| 1 | 0 | 0 | 0             |

| 1 | 0 | 1 | 0             |

| 1 | 1 | 0 | 1             |

| 1 | 1 | 1 | 1             |

Standard  $SOP_{(MINTERMS)} =$

Standard  $POS_{(MAXTERMS)} =$

Part C (9 points) Translate the following standard sum of products (which uses minterms) to the equivalent standard product of sums (using maxterms) by first filling in the truth table below and then deriving the standard product of sums from it.

Standard SOP<sub>(MINTERMS)</sub> =  $A \overline{B} \overline{C} + \overline{A} B \overline{C} + \overline{A} \overline{B} C + \overline{A} B C + A B C$

| A | В | C | $F_{(A,B,C)}$ |

|---|---|---|---------------|

| 0 | 0 | 0 |               |

| 0 | 0 | 1 |               |

| 0 | 1 | 0 |               |

| 0 | 1 | 1 |               |

| 1 | 0 | 0 |               |

| 1 | 0 | 1 |               |

| 1 | 1 | 0 |               |

| 1 | 1 | 1 |               |

Standard  $POS_{(MAXTERMS)} =$

Exam One

5 February 2019

Problem 3 (3 parts, 30 points)

Mixed Logic Reengineering

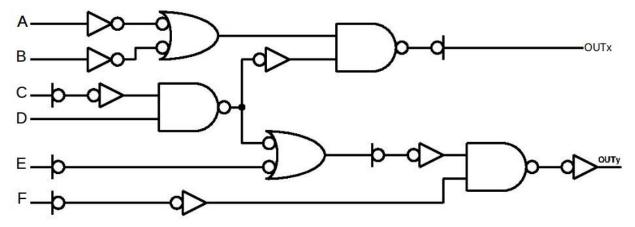

Part A (10 points) Write the output expression for the gate design shown above. Also determine the number of transistors used in its implementation.

Part B (10 points) Reimplement the behavior below with a mixed logic design style using only NOR gates and inverters. Determine the number of switches used in this implementation.

# transistors =

4 problems, 7 pages

Exam One

5 February 2019

Part C (10 points) Implement the following expression using *only* OR gates and inverters. Then determine the number of transistors required. Use proper mixed logic notation. Do not modify the expression. Do not assume complements of inputs are available.

$$Out_Z = \overline{\overline{A} \cdot \overline{B} + \overline{C \cdot D}} + E$$

Exam One

5 February 2019

Problem 4 (2 parts, 20 points)

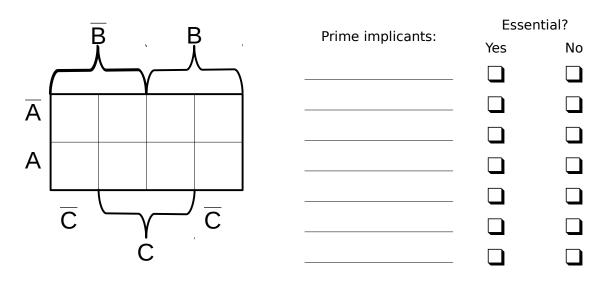

Karnaugh Maps

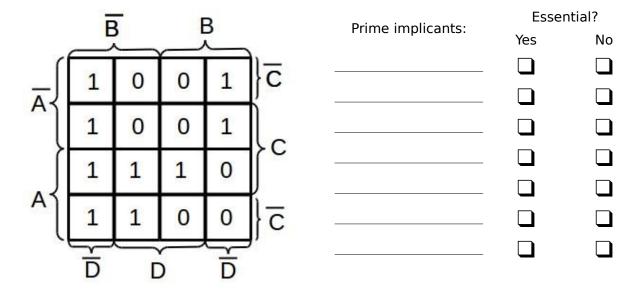

Part A (10 points) Given the following Karnaugh Map, circle and list all the prime implicants, indicating which are essential and write the simplified *sum-of-products* (SOP) expression.

simplified *SOP* expression

Part B (10 points) Simplify the following SOP expression using a Karnaugh Map. Circle and list all the prime implicants, indicating which are essential and write the *product-of-sums* (POS) expression.

$$Out = \overline{A} \, \overline{B} \, C + \overline{A} \, \overline{B} \, \overline{C} + \overline{A} \, B \, \overline{C}$$

Simplified *POS* expression