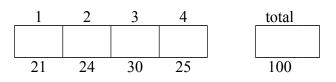

| ECE 2020B           | Fundamentals of Digital Design | Spring 2014      |

|---------------------|--------------------------------|------------------|

| 4 problems, 6 pages | Exam Two                       | 26 February 2014 |

*Instructions:* This is a closed book, closed note exam. Calculators are not permitted. If you have a question, raise your hand and I will come to you. Please work the exam in pencil and do not separate the pages of the exam. For maximum credit, show your work. *Good Luck!*

Your Name (*please print*)

4 problems, 6 pages

Exam Two

## Problem 1 (4 parts, 21 points)

Encoders and Pass Gates

Part A (8 points) Suppose the circuit below has the following input priority:  $I_1 > I_3 > I_0 > I_2$ . Complete the truth table by filling in the input values that would produce the given outputs and derive a simplified expression for  $O_1$ .

|                                                                               | $I_3$ | $I_2$ | $I_1$ | Io | V | $O_1$ | <i>O</i> <sub>0</sub> |

|-------------------------------------------------------------------------------|-------|-------|-------|----|---|-------|-----------------------|

| 4 <sub>0</sub>                                                                |       |       |       |    | 0 | Х     | X                     |

| $-I_0 \frac{1}{5}$ $-I_1 \sim O_0$                                            |       |       |       |    | 1 | 0     | 0                     |

|                                                                               |       |       |       |    | 1 | 0     | 1                     |

| $-I_{2} \operatorname{encode}_{O_{1}}$ $-I_{3} \operatorname{encode}_{O_{1}}$ |       |       |       |    | 1 | 1     | 0                     |

|                                                                               |       |       |       |    | 1 | 1     | 1                     |

## *O*<sub>1</sub> =

Part B (3 points) Consider a priority encoder with the following behavior:

| In <sub>2</sub> | $In_1$ | $In_0$ | Valid | $Out_1$ | $Out_0$ |

|-----------------|--------|--------|-------|---------|---------|

| 0               | 0      | 0      | 0     | х       | Х       |

| 0               | 0      | 1      | 1     | 0       | 0       |

| 0               | 1      | 0      | 1     | 0       | 1       |

| 0               | 1      | 1      | 1     | 0       | 1       |

| 1               | 0      | 0      | 1     | 1       | 0       |

| 1               | 0      | 1      | 1     | 0       | 0       |

| 1               | 1      | 0      | 1     | 0       | 1       |

| 1               | 1      | 1      | 1     | 0       | 1       |

|                 |        |        |       |         |         |

List the inputs (In<sub>0</sub>, In<sub>1</sub>, and In<sub>2</sub>) in decreasing priority.

Part C (6 points) Implement a 2-input XOR gate with pass gates and inverters only. (Hint: remember that a 2-input XOR is a selective inverter.)

Part D (4 points) Does your implementation of an XOR in Part C require fewer transistors than the gate's standard switch-level implementation? Circle one: Yes / No

Support your answer by giving the transistor count for each:

*#* transistors in Part C implementation: *#* transistors in switch-level XOR implementation:

| ECE 2020B                                                          | Fundamentals of Digital Design | Spring 2014      |

|--------------------------------------------------------------------|--------------------------------|------------------|

| 4 problems, 6 pages                                                | Exam Two                       | 26 February 2014 |

| Problem 2 (3 parts, 24 points)<br>Part A (10 points) Convert the f | following notations:           | Number Systems   |

| binary notation                                                    | decimal notation               |                  |

| 0101 1101.1                                                        |                                |                  |

|                                                                    | 52.25                          |                  |

| 110 0110 101                                                       |                                |                  |

octal notation 453.25

Part B (8 points) For the 26 bit representations below, determine the most positive value and the step size (difference between sequential values). **Express all answers in decimal notation**. Fractions (e.g., 3/16ths) may be used. Signed representations are two's complement.

| representation       | most positive value | step size |

|----------------------|---------------------|-----------|

| unsigned integer     |                     | •         |

| (26 bits) . (0 bits) |                     |           |

| signed fixed-point   |                     |           |

| (19 bits) . (7 bits) |                     |           |

| signed integer       |                     |           |

| (26 bits) . (0 bits) |                     |           |

| signed fixed-point   |                     |           |

| (23 bits) . (3 bits) |                     |           |

Part C (6 points) A 20 bit floating point representation has a 12 bit mantissa field, a 7 bit exponent field, and one sign bit.

| What is the largest value that can be represented (closest to infinity)? | 2 |

|--------------------------------------------------------------------------|---|

| What is the smallest value that can be represented (closest to zero)?    | 2 |

How many decimal significant figures are supported?

hexadecimal notation

0xB357.6C

| ECE 2020B                      | Fundamentals of Digital Design                                            | Spring 2014 |  |  |  |  |  |

|--------------------------------|---------------------------------------------------------------------------|-------------|--|--|--|--|--|

| 4 problems, 6 pages            | 4 problems, 6 pages Exam Two                                              |             |  |  |  |  |  |

|                                |                                                                           |             |  |  |  |  |  |

| Problem 3 (3 parts, 30 points  | )                                                                         | Computation |  |  |  |  |  |

| and indicate whether an over   | bblem below, compute the operations<br>flow occurs assuming all numbers a |             |  |  |  |  |  |

| unsigned and six bit two's con | L 1                                                                       |             |  |  |  |  |  |

| 10010                          | 01 10101 110                                                              | 111 11100   |  |  |  |  |  |

| L 1010                         | 11 + 101100 = 011                                                         | 001 10100   |  |  |  |  |  |

|                    | +101011 | + 101100 | <u>- 011001</u> | <u>- 10100</u> |

|--------------------|---------|----------|-----------------|----------------|

| result             |         |          |                 |                |

| unsigned<br>error? |         |          |                 |                |

| signed<br>error?   |         |          |                 |                |

Part B (8 points) For each bit string below, what is the decimal number it represents if it uses a 5-bit unsigned representation and if it uses a 5-bit two's complement representation?

| Bit string | Decimal (if unsigned representation) | Decimal (if 2's complement signed representation) |

|------------|--------------------------------------|---------------------------------------------------|

| 01101      |                                      |                                                   |

| 11110      |                                      |                                                   |

| 1111.1     |                                      |                                                   |

| 011.11     |                                      |                                                   |

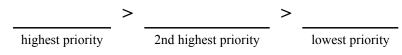

Part C (10 points) Consider the circuit below. Complete the truth table by filling in the empty boxes. (Note that there may be multiple possible inputs that can result in a given output; you need to show only one.) Finally, state what condition this circuit tests on the two input words **A** and **B** (which are each 3-bit words:  $A_2A_1A_0$  and  $B_2B_1B_0$ ).

This circuit's **Out** signal is high if **A**\_\_\_\_\_**B**.

| ECE 2020B           | Fundamentals of Digital Design | Spring 2014      |

|---------------------|--------------------------------|------------------|

| 4 problems, 6 pages | Exam Two                       | 26 February 2014 |

Decoding

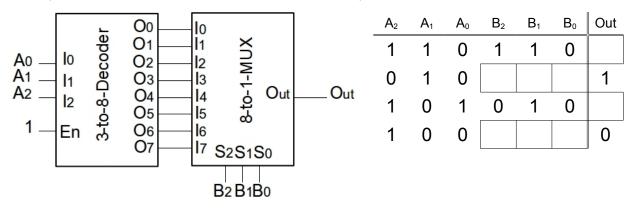

## Problem 4 (4 parts, 25 points)

Suppose you are implementing a seven segment display as shown below. Input decimal numbers are represented as unsigned binary numbers DCBA (e.g., 0101 = 5, which is displayed by lighting segments **a**, **c**, **d**, **f**, and **g**). In this problem, unlike the Homework 2 problem, assume that for input decimal numbers greater than 9, the 7-segment display is blank (no segments are lit up).

**Part A** (4 points) Complete the BCD to 7-segment decoder truth table below by filling in the Decoder Output column for **a**.

| I | <b>Binary Inputs</b> |   |   | Decoder Outputs |   |   |   |   |   |   | 7-Segment Display Outputs |

|---|----------------------|---|---|-----------------|---|---|---|---|---|---|---------------------------|

| D | С                    | В | A | a               | b | c | d | e | f | g |                           |

| 0 | 0                    | 0 | 0 |                 | 1 | 1 | 1 | 1 | 1 | 0 | 0                         |

| 0 | 0                    | 0 | 1 |                 | 1 | 1 | 0 | 0 | 0 | 0 | 1                         |

| 0 | 0                    | 1 | 0 |                 | 1 | 0 | 1 | 1 | 0 | 1 | 2                         |

| 0 | 0                    | 1 | 1 |                 | 1 | 1 | 1 | 0 | 0 | 1 | 3                         |

| 0 | 1                    | 0 | 0 |                 | 1 | 1 | 0 | 0 | 1 | 1 | 4                         |

| 0 | 1                    | 0 | 1 |                 | 0 | 1 | 1 | 0 | 1 | 1 | 5                         |

| 0 | 1                    | 1 | 0 |                 | 0 | 1 | 1 | 1 | 1 | 1 | 6                         |

| 0 | 1                    | 1 | 1 |                 | 1 | 1 | 0 | 0 | 0 | 0 | 7                         |

| 1 | 0                    | 0 | 0 |                 | 1 | 1 | 1 | 1 | 1 | 1 | 8                         |

| 1 | 0                    | 0 | 1 |                 | 1 | 1 | 1 | 0 | 1 | 1 | 9                         |

| 1 | 0                    | 1 | x | 0               | 0 | 0 | 0 | 0 | 0 | 0 | no segments turned on     |

| 1 | 1                    | х | x | 0               | 0 | 0 | 0 | 0 | 0 | 0 | no segments turned on     |

Part B (6 points) Write the standard sum of products form of Decoder Output e.

e =

**Part C** (6 points) For which decimal numbers is the following expression true? Assume each decimal number is represented as an unsigned binary number DCBA.

$W = \overline{D} + \overline{B} \cdot \overline{C}$

Decimal numbers:

| ECE 2020B           | Fundamentals of Digital Design | Spring 2014      |

|---------------------|--------------------------------|------------------|

| 4 problems, 6 pages | Exam Two                       | 26 February 2014 |

|                     |                                |                  |

**Part D** (9 points) Implement Decoder Output **e** using a single 4-to-16 decoder (with an enable) and a single OR gate. The OR gate may have any number of inputs that you need. Label all input and output signals on the decoder. Assume you are given the inputs A, B, C, D, and the input  $W = \overline{D} + \overline{B} \cdot \overline{C}$  (which is provided by another circuit that you do not need to implement).

D+BC=W—