*Instructions:* This is a closed book, closed note exam. Calculators are not permitted. If you have a question, raise your hand and I will come to you. Please work the exam in pencil and do not separate the pages of the exam. For maximum credit, show your work. *Good Luck!*

Your Name (*please print*)

## Computer Engineering

Spring 2012

4 problems, 6 pages

Exam Three

12 April 2012

| Problem 1         | (3  | parts. | 30 | points' | Ì |

|-------------------|-----|--------|----|---------|---|

| I I C C I C I I I | ( - | parts, |    | POILIED | , |

Memory Systems

**Part A** (12 points) Consider a **1 Gbit** DRAM chip organized as **32 million addresses** of **32-bit words**. Assume both the DRAM cell and the DRAM chip are square. The column number and offset concatenate to form the memory address. Using the organization approach discussed in class, answer the following questions about the chip. *Express all answers in decimal (not powers of two)*.

| total number of bits in address                                                     |                                                                       |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| number of columns                                                                   |                                                                       |

| column decoder required $(n \text{ to } m)$                                         |                                                                       |

| number of words per column                                                          |                                                                       |

| type of mux required $(n \text{ to } m)$                                            |                                                                       |

| number of address lines in column offse                                             | et                                                                    |

| Part B (10 points) Consider an 8 Gbyte med 32 million address by 32-bit word memory | mory system with 1 billion addresses of 64-bit words using DRAM chip. |

| word address lines for memory system _                                              |                                                                       |

| chips needed in one bank                                                            |                                                                       |

| banks for memory system                                                             |                                                                       |

| memory decoder required $(n \text{ to } m)$                                         |                                                                       |

| DRAM chips required                                                                 |                                                                       |

**Part** C (8 points) Design a **16 million address by 4 bit** memory system with **4 million x 4** memory chips. *Label all busses and indicate bit width*. Assume R/W is connected and not shown here. Use a bank decoder if necessary. Be sure to include the address bus, data bus, and MSEL.

12 April 2012

Problem 2 (3 parts, 26 points)

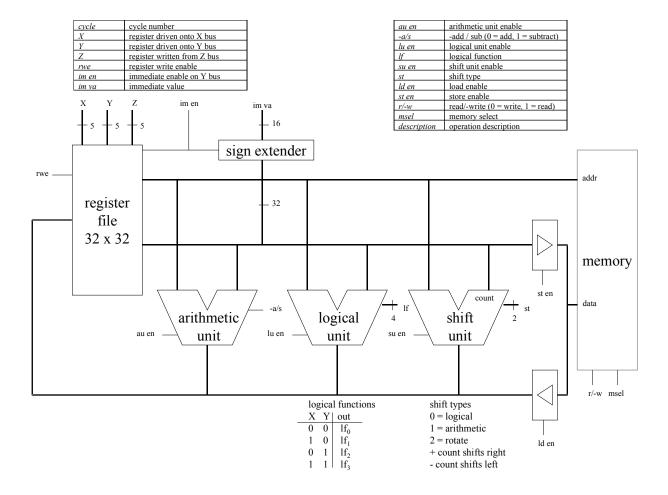

**Datapath Elements**

Part A (6 points) Suppose the following inputs (in hexadecimal) are applied to the 32-bit barrel shifter used in the datapath. Determine the output (in hexadecimal). Assume the shift amount is drawn from the 16-bit immediate value.

| Shift Type | Shift Amount | Input Value | Output Value |

|------------|--------------|-------------|--------------|

| arithmetic | 0x0008       | ABCD12EF    |              |

| rotate     | 0xFFF4       | DEAF7892    |              |

| arithmetic | 0xFFF0       | FACE2537    |              |

**Part B** (8 points) For each bitwise logical function specification below, determine the LF code (in hexadecimal) to correctly program the logical unit.

| ΧΥ  | Out             |

|-----|-----------------|

| 0 0 | LF <sub>0</sub> |

| 1 0 | LF <sub>1</sub> |

| 0 1 | LF <sub>2</sub> |

| 1 1 | LF <sub>3</sub> |

| logical function | LF |

|------------------|----|

| Y + X            |    |

| X                |    |

| $X \oplus Y$     |    |

| $X \cdot Y$      |    |

Part C (12 points) Given the following state table, draw the corresponding state diagram below.

|       | <u> </u> |     |        |        |     |       |       |     | <u>.                                    </u> |                 |     |

|-------|----------|-----|--------|--------|-----|-------|-------|-----|----------------------------------------------|-----------------|-----|

| $S_1$ | $S_0$    | H/M | $NS_1$ | $NS_0$ | Out | $S_1$ | $S_0$ | H/M | $NS_1$                                       | NS <sub>0</sub> | Out |

| 0     | 0        | 0   | 0      | 1      | 0   | 1     | 0     | 0   | 0                                            | 0               | 1   |

| 0     | 0        | 1   | 0      | 0      | 0   | 1     | 0     | 1   | 0                                            | 0               | 0   |

| 0     | 1        | 0   | 1      | 0      | 0   | 1     | 1     | 0   | x                                            | x               | x   |

| 0     | 1        | 1   | 0      | 0      | 0   | 1     | 1     | 1   | x                                            | x               | x   |

| Give | the simi | nlified | Roolean | expression 1 | for com   | nutino | NS.  | in terms    | of the | current | state a | nd the | ∍ inr | nit  |

|------|----------|---------|---------|--------------|-----------|--------|------|-------------|--------|---------|---------|--------|-------|------|

| OIVC | the sim  | Dillica | Doorcan | CADICSSIUII  | IOI COIII | Duung  | 1101 | 111 (C11113 | or the | Current | state a | na un  | . III | Jui. |

Exam Three

12 April 2012

Problem 3 (3 parts, 26 points)

Microcode

Using the supplied datapath, write microcode fragments to accomplish the following procedures. Express all values, except memory addresses, in hexadecimal notation. Use 'X' when a value is don't cared. For maximum credit, complete the description field. In each part, modify only registers 7 & 8.

Part A (5 points)

$R_7 = (R_8 - 12)/128$

| # | X | Y | Z | rwe | im<br>en | im va | au<br>en | $\frac{s}{a}$ | lu<br>en | lf | su<br>en | st | ld<br>en | st<br>en | $\frac{r/}{w}$ | msel | description |

|---|---|---|---|-----|----------|-------|----------|---------------|----------|----|----------|----|----------|----------|----------------|------|-------------|

| 1 |   |   |   |     |          |       |          |               |          |    |          |    |          |          |                |      |             |

| 2 |   |   |   |     |          |       |          |               |          |    |          |    |          |          |                |      |             |

| 3 |   |   |   |     |          |       |          |               |          |    |          |    |          |          |                |      |             |

Part B (15 points) Compute the logical OR of mem[4000] and  $R_3$  and store the result in

mem[4004] (that is mem[4004] gets mem[4000]+R<sub>2</sub> where "+" is "logical or")

| IIIC | ոոլ- | 1005 | ք] (ե | 11at 15 | , mc | 111[4004 | · j gci | 2 111     | տոլե | 1000 | /]   IX3 | , wı | ICIC | ' 1 | 5 10      | gicai | 01 ).       |

|------|------|------|-------|---------|------|----------|---------|-----------|------|------|----------|------|------|-----|-----------|-------|-------------|

| #    | X    | Y    | Z     | rwe     | im   | im va    | аи      | <u>s/</u> | lu   | lf   | su       | st   | ld   | st  | <u>r/</u> | msel  | description |

|      |      |      |       |         | en   |          | en      | а         | en   |      | en       |      | en   | en  | W         |       |             |

| 1    |      |      |       |         |      |          |         |           |      |      |          |      |      |     |           |       |             |

|      |      |      |       |         |      |          |         |           |      |      |          |      |      |     |           |       |             |

| 2    |      |      |       |         |      |          |         |           |      |      |          |      |      |     |           |       |             |

|      |      |      |       |         |      |          |         |           |      |      |          |      |      |     |           |       |             |

| 3    |      |      |       |         |      |          |         |           |      |      |          |      |      |     |           |       |             |

|      |      |      |       |         |      |          |         |           |      |      |          |      |      |     |           |       |             |

| 4    |      |      |       |         |      |          |         |           |      |      |          |      |      |     |           |       |             |

| 4    |      |      |       |         |      |          |         |           |      |      |          |      |      |     |           |       |             |

| 5    |      |      |       |         |      |          |         |           |      |      |          |      |      |     |           |       |             |

| ا    |      |      |       |         |      |          |         |           |      |      |          |      |      |     |           |       |             |

|      |      |      |       |         |      |          |         |           |      |      |          |      |      |     |           |       |             |

| 6    |      |      |       |         |      |          |         |           |      |      |          |      |      |     |           |       |             |

Part C (6 points)

$R_7 = 15 \cdot R_8$  (multiply R<sub>8</sub> by 15)

| # | X | Y | Z | rwe | im | im va | аи | <u>s</u> / | lu | lf | su | st | ld | st | <u>r/</u> | msel | description |

|---|---|---|---|-----|----|-------|----|------------|----|----|----|----|----|----|-----------|------|-------------|

|   |   |   |   |     | en |       | en | а          | en |    | en |    | en | en | w         |      |             |

| 1 |   |   |   |     |    |       |    |            |    |    |    |    |    |    |           |      |             |

| 2 |   |   |   |     |    |       |    |            |    |    |    |    |    |    |           |      |             |

| 3 |   |   |   |     |    |       |    |            |    |    |    |    |    |    |           |      |             |

| 4 |   |   |   |     |    |       |    |            |    |    |    |    |    |    |           |      |             |

Spring 2012

4 problems, 6 pages

Exam Three

12 April 2012

Problem 4 (2 parts, 18 points)

Counters

Part A (8 points) Design a toggle cell using *only transparent latches and basic gates (XOR, AND, OR, NAND, NOR, NOT)*. Use an icon for the transparent latches. Your toggle cell should have an active high toggle enable input **TE**, and an active low clear input  $\overline{CLR}$ , clock inputs  $\Phi_1$  and  $\Phi_2$ , and an output **Out**. The  $\overline{CLR}$  signal has precedence over **TE**. Label all signals. Also complete the behavior table for the toggle cell.

| TE | $\overline{CLR}$ | CLK                   | Out |

|----|------------------|-----------------------|-----|

| 0  | 0                | $\uparrow\downarrow$  |     |

| 1  | 0                | $\uparrow \downarrow$ |     |

| 0  | 1                | $\uparrow\downarrow$  |     |

| 1  | 1                | $\uparrow\downarrow$  |     |

Part B (10 points) Now combine these toggle cells to build a **divide by thirteen** counter. Your counter should have an external clear, external count enable, and four count outputs O<sub>3</sub>, O<sub>2</sub>, O<sub>1</sub>, O<sub>0</sub>. Use any basic gates (AND, OR, NAND, NOR, XOR & NOT) you require. Assume clock inputs to the toggle cells are already connected. Your design must support multi-digit systems.

| Ext CE —  | TE<br>Out<br>CLR | - O <sub>0</sub> |

|-----------|------------------|------------------|

|           | TE<br>Out<br>CLR | - O <sub>1</sub> |

|           | TE<br>Out<br>CLR | - O <sub>2</sub> |

| Ext CLR — | TE<br>Out<br>CLR | - O <sub>3</sub> |

4 problems, 6 pages

Exam Three

12 April 2012