| ECE 2030D           | Computer Engineering | Spring 2012  |

|---------------------|----------------------|--------------|

| 4 problems, 5 pages | Exam Two             | 8 March 2012 |

*Instructions:* This is a closed book, closed note exam. Calculators are not permitted. If you have a question, raise your hand and I will come to you. Please work the exam in pencil and do not separate the pages of the exam. For maximum credit, show your work. *Good Luck!*

Your Name (*please print*)

| ECE 2030D                      | Computer Engineering             | Spring 2012     |

|--------------------------------|----------------------------------|-----------------|

| 4 problems, 5 pages            | Exam Two                         | 8 March 2012    |

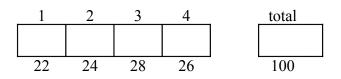

| Problem 1 (4 parts, 22 points) |                                  | Building Blocks |

| Part A (6 points) Implement a  | 2 to 4 decoder with basic gates. |                 |

| $I_0$ ——                       |                                  | $ O_0$          |

|                                |                                  |                 |

| $I_1$ —                        |                                  | $O_1$           |

|                                |                                  | -               |

| EN —                           |                                  | $O_2$           |

|                                |                                  |                 |

|                                |                                  | $O_3$           |

Part B (8 points) Suppose the circuit below has the following input priority:  $I_0 > I_2 > I_3 > I_1$ . Complete the truth table by filling in the input values that would produce the given outputs and derive a simplified expression for  $O_1$ .

|                                                                                                                       | $I_3$ | $I_2$ | $I_1$ | I <sub>0</sub> | V | $O_1$ | <i>O</i> <sub>0</sub> |

|-----------------------------------------------------------------------------------------------------------------------|-------|-------|-------|----------------|---|-------|-----------------------|

| 4 .                                                                                                                   |       |       |       |                | 0 | Х     | Х                     |

| $-10 \overrightarrow{5}$<br>$-11 \approx 00$                                                                          |       |       |       |                | 1 | 0     | 0                     |

|                                                                                                                       |       |       |       |                | 1 | 0     | 1                     |

| $ \begin{array}{c} -I_{0} \stackrel{4}{} \\ +I_{0} \\ -I_{1} \\ +I_{2} \\ -I_{2} \\ -I_{3} \\ -I_{3} \\ \end{array} $ |       |       |       |                | 1 | 1     | 0                     |

|                                                                                                                       |       |       |       |                | 1 | 1     | 1                     |

*O*<sub>1</sub> = \_\_\_\_\_

Part C (4 points) Which basic gate, having inputs X and Y, does the following circuit implement? Hint: Complete the truth table at the right. L

| 1 - 10               |       | Х | У | Out |

|----------------------|-------|---|---|-----|

| 1 10<br>Mux<br>0 11  |       | 0 | 0 |     |

| 0 — 11<br>0 — 12 Out | — Out | 0 | 1 |     |

| 0 — 13<br>S0 S1      |       | 1 | 0 |     |

| X Y                  |       | 1 | 1 |     |

## This implements a \_\_\_\_\_\_.

Part D (4 points) If the mux in Part C is implemented with pass gates and inverters, does the implementation of the basic gate in Part C require fewer transistors than the gate's standard switch-level implementation?

Circle one: Yes / No

## Support your answer by giving the transistor count for each:

# transistors in MUX implementation: # transistors in switch-level implementation:

| ECE 2030D                      | Computer Engineering | Spring 2012    |

|--------------------------------|----------------------|----------------|

| 4 problems, 5 pages            | Exam Two             | 8 March 2012   |

| Problem 2 (3 parts, 24 points) |                      | Number Systems |

Part A (10 points) Convert the following notations:

| binary notation      | decimal notation |  |

|----------------------|------------------|--|

| 1100 0101.           |                  |  |

|                      | 21.625           |  |

| 1 1001.011           |                  |  |

| hexadecimal notation | octal notation   |  |

|                      | 754.26           |  |

| D5.A                 |                  |  |

Part B (8 points) For the 12 bit representations below, determine the most positive value and the step size (difference between sequential values). **Express all answers in decimal notation**. Fractions (e.g., 3/16ths) may be used. Signed representations are two's complement.

| representation                             | most positive value | step size |

|--------------------------------------------|---------------------|-----------|

| unsigned integer                           |                     |           |

| (12 bits) . (0 bits)<br>signed fixed-point |                     |           |

| (7 bits) . (5 bits)                        |                     |           |

| signed integer                             |                     |           |

| (12 bits) . (0 bits)                       |                     |           |

| signed fixed-point<br>(9 bits). (3 bits)   |                     |           |

Part C (6 points) A 16 bit floating point representation has a 10 bit mantissa field, a 5 bit exponent field, and one sign bit.

| What is the largest value that can be represented (closest to infinity)? | 2 |

|--------------------------------------------------------------------------|---|

| What is the smallest value that can be represented (closest to zero)?    | 2 |

How many decimal significant figures are supported?

| ECE 2030D          |                 | Computer Engin | Spring 2012      |                                                       |

|--------------------|-----------------|----------------|------------------|-------------------------------------------------------|

| 4 problems, 5 pag  | es              | Exam Two       | )                | 8 March 2012                                          |

|                    |                 |                |                  |                                                       |

| Problem 3 (3 parts | s, 28 points)   |                |                  | Adding & Subtracting                                  |

| and indicate wheth | ner an overflow |                | 1 numbers are ex | g the rules of arithmetic,<br>pressed using a six bit |

| 5                  | 101010          | 11011          | 111000           | 101000                                                |

|                    | + 11000         | + 1010         | - 110110         | <u>- 1011</u>                                         |

| result             |                 |                |                  |                                                       |

| unsigned           |                 |                |                  |                                                       |

| error?             |                 |                |                  |                                                       |

| signed             |                 |                |                  |                                                       |

| error?             |                 |                |                  |                                                       |

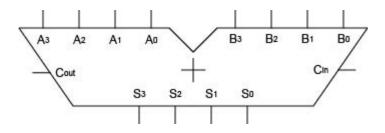

Part B (6 points) The adder below adds two four bit numbers A and B and produces a four bit result S. Add extra digital logic to support subtraction as well as addition. Label inputs  $X_3$ ,  $X_2$ ,  $X_1$ ,  $X_0$ ,  $Y_3$ ,  $Y_2$ ,  $Y_1$ ,  $Y_0$ ,  $\overline{ADD} / SUB$  and outputs  $Z_3$ ,  $Z_2$ ,  $Z_1$ ,  $Z_0$ .

Part C (6 points) Write two Boolean expressions indicating *signed two's complement* addition and subtraction overflow using any of the signals labeled in part B that are necessary. These expressions should be true when overflow occurs.

addition overflow =

subtraction overflow =

Part D (4 points) Write two Boolean expressions indicating *unsigned* addition and subtraction overflow using any of the signals labeled in part B that are necessary. These expressions should be true when overflow occurs.

addition overflow =

subtraction overflow =

| ECE 2030D           | Computer Engineering | Spring 2012  |

|---------------------|----------------------|--------------|

| 4 problems, 5 pages | Exam Two             | 8 March 2012 |

Problem 4 (4 parts, 26 points)

Registers and Latches

Part A (8 points) Implement a transparent latch using only NOR gates, AND gates, and inverters. Label the inputs **In** and **En**, and output **Out**. Do not attempt to employ mixed logic notation. Also complete the truth table.

| _ | In | En | Out |

|---|----|----|-----|

|   | Α  | 0  |     |

|   | Α  | 1  |     |

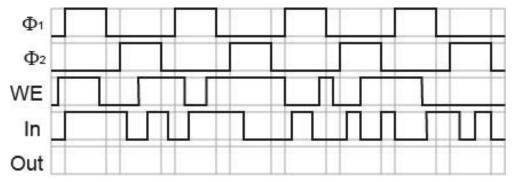

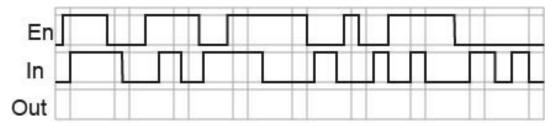

Part B (7 points) Assume the following signals are applied to a transparent latch. Draw the output signal **Out**. Assume **Out** is initially zero.

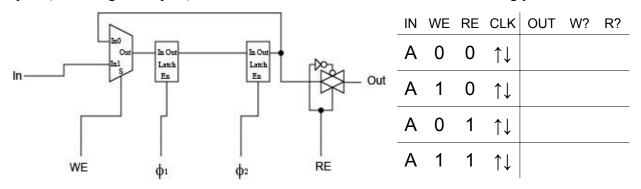

Part C (4 points) Consider a register with a selectable *write enable* (WE) and *read enable* (RE), implemented as shown below. Describe its behavior by completing the output values. Recall that the CLK signal indicates a full  $\Phi_1 \Phi_2$  cycle; so the output should be the value at the end of a cycle (with the given inputs). Also indicate when a write and/or a read is being performed.

Part D (7 points) Assume the following signals are applied to a register with write enable. Draw the output signal **Out**. Draw a vertical line where **In** is sampled. *Assume Out* is *initially zero*.