| ECE 2030 D          | Computer Engineering | Spring 2012     |

|---------------------|----------------------|-----------------|

| 4 problems, 5 pages | Exam One             | 9 February 2012 |

*Instructions:* This is a closed book, closed note exam. Calculators are not permitted. If you have a question, raise your hand and I will come to you. Please work the exam in pencil and do not separate the pages of the exam. For maximum credit, show your work. *Good Luck!*

Your Name (*please print*)

| ECE 2030 D          | Computer Engineering | Spring 2012     |

|---------------------|----------------------|-----------------|

| 4 problems, 5 pages | Exam One             | 9 February 2012 |

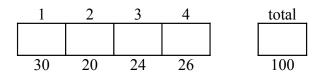

Problem 1 (3 parts, 30 points)

**Incomplete Circuits**

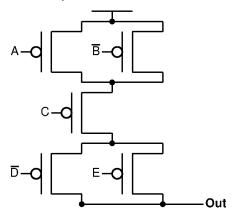

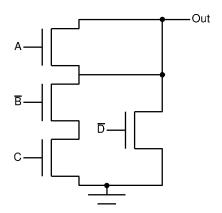

The three parts below contain (A) a pull up network, (B) a pull down network, and (C) an expression to be implemented. For (A) and (B), complete the missing complementary switching networks so the circuit contains no floats or shorts and write the Boolean expression computed by the completed circuit. For (C), design the entire switching network. Assume the inputs and their complements are available.

OUTx =

OUTy =

$OUTz = A \cdot (\overline{D} + \overline{B} \cdot C)$

| ECE 2030 D          | Computer Engineering | Spring 2012     |

|---------------------|----------------------|-----------------|

| 4 problems, 5 pages | Exam One             | 9 February 2012 |

Problem 2 (2 parts, 20 points)

Boolean Algebra

Part A (12 points) Transform each of the following Boolean expressions to a form where they are ready for switch level implementation (i.e., there should only be bars over input variables, not over operations). The behavior of the expression should remain unchanged. **Do not implement**.

\_\_\_\_\_

$OUT_{X} = \overline{\overline{A} \cdot B + (C + \overline{D} \cdot E)} + \overline{\overline{F} + G}$

$$OUT_{Y} = \overline{\overline{G \cdot H} \cdot (\overline{K} \cdot \overline{L \cdot M} + N \cdot P)}$$

Part B (8 points) Derive a canonical sum of products (using minterms) and a product of sums (using maxterms) expression for the truth table below.

| А | В | С | F <sub>(A,B,C)</sub> |

|---|---|---|----------------------|

| 0 | 0 | 0 | 1                    |

| 1 | 0 | 0 | 1                    |

| 0 | 1 | 0 | 1                    |

| 1 | 1 | 0 | 0                    |

| 0 | 0 | 1 | 1                    |

| 1 | 0 | 1 | 0                    |

| 0 | 1 | 1 | 0                    |

| 1 | 1 | 1 | 0                    |

Standard  $SOP_{(MINTERMS)} =$

Standard  $POS_{(MAXTERMS)} =$

| ECE 2030 D          | Computer Engineering | Spring 2012     |

|---------------------|----------------------|-----------------|

| 4 problems, 5 pages | Exam One             | 9 February 2012 |

Problem 3 (2 parts, 24 points)

Karnaugh Maps

Part A (12 points) For the following expression, derive a simplified *sum of products* expression using a Karnaugh Map. Circle and list *all* prime implicants, indicating which are essential.

$Out = (A + C + \overline{D}) \cdot (\overline{A} + B + D) \cdot (\overline{A} + B + C) \cdot (\overline{A} + \overline{B} + D)$

simplified SOP expression

Part B (12 points) For the following expression, derive a simplified *product of sums* expression using a Karnaugh Map. Circle and list all prime implicants, indicating which are essential.

$Out = \overline{B} \cdot \overline{C} \cdot D + \overline{A} \cdot B \cdot D + B \cdot C \cdot \overline{D} + \overline{B} \cdot C \cdot \overline{D}$

simplified POS expression

| ECE 2030 D          | Computer Engineering | Spring 2012     |

|---------------------|----------------------|-----------------|

| 4 problems, 5 pages | Exam One             | 9 February 2012 |

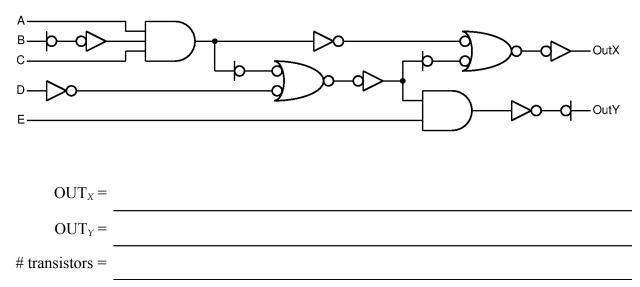

Problem 4 (2 parts, 26 points)

Mixed Logic Design

Part A (12 points) The following design has no supporting documentation. Derive the desired Boolean expression and the implementation cost (in CMOS transistors). Do not simplify the expressions.

Part B (14 points) Now reimplement these expressions using NAND gates and inverters. Use proper mixed logic notation. Determine the cost of this implementation (in transistors).

# transistors =