| ECE 2030 A 10:00am  | Computer Engineering | Spring 2010        |

|---------------------|----------------------|--------------------|

| 5 problems, 7 pages | Final Exam           | Cinco de Mayo 2010 |

*Instructions:* This is a closed book, closed note exam. Calculators are not permitted. If you have a question, raise your hand and I will come to you. Please work the exam in pencil and do not separate the pages of the exam. For maximum credit, show your work. *Good Luck!*

Your Name (*please print*)

| ECE 2030 A 1<br>5 problems, 7 |                 | Con            | nputer Engineeri<br>Final Exam | ing            | Spring 2010<br>Cinco de Mayo 2010 |

|-------------------------------|-----------------|----------------|--------------------------------|----------------|-----------------------------------|

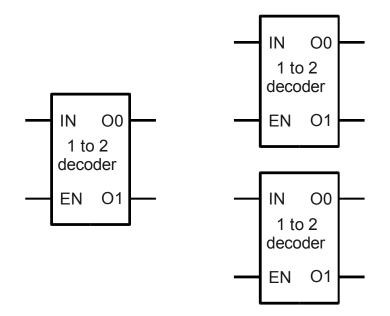

| Problem 1 (3 pa               | , <b>1</b>      |                |                                |                | Decoding Decoders                 |

| Part A (6 points              | b) Define a 1 t | o 2 decoder by | completing the l               | behavior table |                                   |

| IN                            | EN              | O0             | 01                             |                | IN 00                             |

| Х                             | 0               |                |                                |                | 1 to 2<br>decoder                 |

| 0                             | 1               |                |                                |                | EN 01                             |

| 1                             | 1               |                |                                |                |                                   |

Part B (8 points) Implement a 1 to 2 decoder using basic gates. Assume only true (non-complemented) inputs are available. Label all inputs and outputs.

Part C (10 points) Using *only* the three 1 to 2 decoders shown below, implement a 2 to 4 decoder with an enable. Label the decoder inputs ( $IN_1$ ,  $IN_0$ , EN) and outputs (O0, O1, O2, O3).

| ECE 2030 A 10:00am<br>5 problems, 7 pages                                                                              | Computer Engineering<br>Final Exam                                       | Spring 2010<br>Cinco de Mayo 2010                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Problem 2 (4 parts, 30 points)<br>Complete each design below. Be sure                                                  | to label all signals.                                                    | Design Fiesta                                                                                                                                                                   |

| Part A: Implement the following expression<br>P type switches. $Out_X = (\overline{A} + B \cdot \overline{C}) \cdot D$ | using N and Part B: Implement the pass gates and inverter                | the following behavior using only<br>rs.<br>$\begin{array}{c c} X & Y & Z & \overline{Z} \\ \hline A & 0 & Q_0 & \overline{Q}_0 \\ \hline A & 1 & A & \overline{A} \end{array}$ |

| Part C: Determine the appropriate express<br>mixed logic design. How many transistors ar                               | ion for this Part D: Reimplement<br>nerequired? NAND and NOT garequired? | the design in Part D using <i>only</i> ates. How many transistors are                                                                                                           |

|                                                                                                                        | ☐<br>)—Out                                                               |                                                                                                                                                                                 |

| Out =                                                                                                                  |                                                                          |                                                                                                                                                                                 |

| # transistors =                                                                                                        | # transistors =                                                          |                                                                                                                                                                                 |

| ECE 2030 A 10:00am  | Computer Engineering | Spring 2010        |

|---------------------|----------------------|--------------------|

| 5 problems, 7 pages | Final Exam           | Cinco de Mayo 2010 |

Problem 3 (1 part, 25 points)

Assembly Programming

**Part A** (25 points) Complete this subroutine that searches an array of 100 integers beginning at memory address 5000 and returns its minimum (\$4) and maximum (\$5) values. Use the following registers: \$1= array pointer, \$2= end address, \$3= current value, \$6= branch predicate.

| label   | instruction | comment                           |

|---------|-------------|-----------------------------------|

| MinMax: |             | <pre># init array ptr</pre>       |

|         |             | <pre># set end address</pre>      |

|         |             | # init min                        |

|         |             | # init max                        |

|         |             | <pre># load current element</pre> |

|         |             | <pre># if current &gt;= min</pre> |

|         |             | # then skip update                |

|         |             | # update min                      |

|         |             | <pre># if current &lt;= max</pre> |

|         |             | # then skip update                |

|         |             | # update max                      |

|         |             | # point to next element           |

|         |             | <pre># if not done, loop</pre>    |

|         | jr \$31     | # return to caller                |

MIPS Instruction Set

| instruction                | example            | meaning                                       |

|----------------------------|--------------------|-----------------------------------------------|

| add                        | add \$1,\$2,\$3    | \$1 = \$2 + \$3                               |

| subtract                   | sub \$1,\$2,\$3    | \$1 = \$2 - \$3                               |

| add immediate              | addi \$1,\$2,100   | \$1 = \$2 + 100                               |

| multiply                   | mul \$1,\$2,\$3    | \$1 = \$2 * \$3                               |

| divide                     | div \$1,\$2,\$3    | \$1 = \$2 / \$3                               |

| and                        | and \$1,\$2,\$3    | \$1 = \$2 & \$3                               |

| or                         | or \$1,\$2,\$3     | \$1 = \$2   \$3                               |

| xor                        | xor \$1,\$2,\$3    | \$1 = \$2 xor \$3                             |

| and immediate              | andi \$1,\$2,100   | \$1 = \$2 & 100                               |

| or immediate               | ori \$1,\$2,100    | \$1 = \$2   100                               |

| xor immediate              | xori \$1,\$2,100   | \$1 = \$2 xor 100                             |

| shift left logical         | sll \$1,\$2,5      | \$1 = \$2 << 5 (logical)                      |

| shift right logical        | srl \$1,\$2,5      | \$1 = \$2 >> 5 (logical)                      |

| shift left arithmetic      | sla \$1,\$2,5      | \$1 = \$2 << 5 (arithmetic)                   |

| shift right arithmetic     | sra \$1,\$2,5      | \$1 = \$2 >> 5 (arithmetic)                   |

| load word                  | lw \$1, (\$2)      | \$1 = memory [\$2]                            |

| store word                 | sw \$1, (\$2)      | memory [\$2] = \$1                            |

| load upper immediate       | lui \$1,100        | $\$1 = 100 \times 2^{16}$                     |

| branch if equal            | beq \$1,\$2,100    | if $(\$1 = \$2)$ , PC = PC + 4 + $(100*4)$    |

| branch if not equal        | bne \$1,\$2,100    | if $(\$1 \neq \$2)$ , PC = PC + 4 + $(100*4)$ |

| set if less than           | slt \$1, \$2, \$3  | if (\$2 < \$3), \$1 = 1 else \$1 = 0          |

| set if less than immediate | slti \$1, \$2, 100 | if (\$2 < 100), \$1 = 1 else \$1 = 0          |

| jump                       | j 10000            | PC = 10000                                    |

| jump register              | jr \$31            | PC = \$31                                     |

| jump and link              | jal 10000          | \$31 = PC + 4; PC = 10000                     |

| ECE 2030 A 10:00am   | Computer Engineering | Spring 2010        |

|----------------------|----------------------|--------------------|

| _5 problems, 7 pages | Final Exam           | Cinco de Mayo 2010 |

"Math is fun"

Problem 4 (4 parts, 36 points)

Part A (9 points) Consider the instruction set architecture below with fields containing zeros.

| 0000 0000 | 00 0000    | 00 000        | 00 0000 0000 0000 0000 |

|-----------|------------|---------------|------------------------|

| opcode    | dest. reg. | source 1 reg. | immediate value        |

What is the maximum number of opcodes?

What is the number of registers?

What is the range of the signed immediate value?

Part B (9 points) For the eight bit representations below, determine the most positive value and the step size (difference between sequential values). All answers should be expressed in decimal notation. Fractions (e.g., 3/16ths) may be used. Signed representations are two's complement.

| representation       | most positive value | step size |

|----------------------|---------------------|-----------|

| unsigned integer     |                     |           |

| (8 bits) . (0 bits)  |                     |           |

| signed fixed-point   |                     |           |

| (6 bits) . (2 bits)  |                     |           |

| unsigned fixed-point |                     |           |

| (0 bits) . (8 bits)  |                     |           |

Part C (6 points) A 48 bit floating point representation has a 37 bit mantissa field, a 10 bit exponent field, and one sign bit.

| What is the largest value that can be represented (closest to infinity)? | 2 |

|--------------------------------------------------------------------------|---|

| What is the smallest value that can be represented (closest to zero)?    | 2 |

How many decimal significant figures are supported?

Part D (12 points) For each problem below, compute the operations using the rules of arithmetic, and indicate whether an overflow occurs assuming all numbers are expressed using a **five bit unsigned fixed-point** and **five bit two's complement fixed-point** representations.

| 0.111  | .0011   | 1010.0          | 0.00            |

|--------|---------|-----------------|-----------------|

| +0.111 | +1.1101 | <u>- 1001.1</u> | <u>- 100.00</u> |

result

| unsigned error? | □ no | □ yes |

|-----------------|------|-------|------|-------|------|-------|------|-------|

| signed error?   | □ no | □ yes |

| ECE 2030 A 10:00am  | Computer Engineering | Spring 2010        |

|---------------------|----------------------|--------------------|

| 5 problems, 7 pages | Final Exam           | Cinco de Mayo 2010 |

## Problem 5 (5 parts, 30 points)

Microcode in Reverse

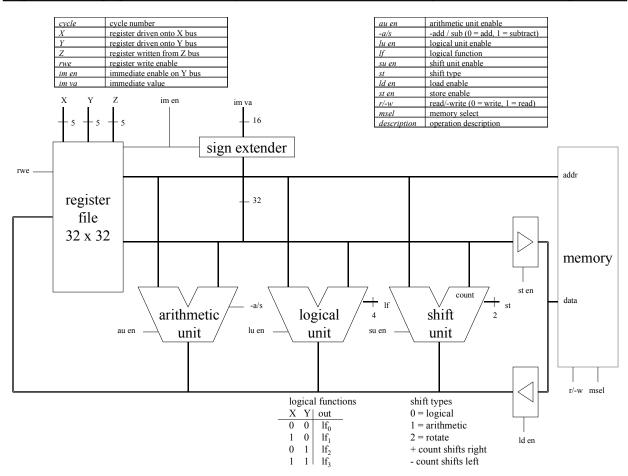

The microcode fragment below comes from a color scanner control program that runs on the datapath discussed in class. Unfortunately, don't care values (X) have been converted to zeros. Assume register zero is a normal register (not hardwired to the value zero).

| #  | X | Y | Ζ | rwe | im<br>en | im va | au<br>en | -a/s | lu<br>en | lf | su<br>en | st | ld<br>en | st<br>en | r/-w | msel |

|----|---|---|---|-----|----------|-------|----------|------|----------|----|----------|----|----------|----------|------|------|

| 1  | 0 | 0 | 3 | 1   | 1        | 4000  | 0        | 0    | 1        | C  | 0        | 0  | 0        | 0        | 0    | 0    |

| 2  | 3 | 0 | 0 | 1   | 0        | 0     | 0        | 0    | 0        | 0  | 0        | 0  | 1        | 0        | 1    | 1    |

| 3  | 0 | 0 | 2 | 1   | 1        | FF    | 0        | 0    | 1        | 8  | 0        | 0  | 0        | 0        | 0    | 0    |

| 4  | 0 | 0 | 0 | 1   | 1        | 8     | 0        | 0    | 0        | 0  | 1        | 0  | 0        | 0        | 0    | 0    |

| 5  | 0 | 0 | 1 | 1   | 1        | FF    | 0        | 0    | 1        | 8  | 0        | 0  | 0        | 0        | 0    | 0    |

| 6  | 1 | 2 | 2 | 1   | 0        | 0     | 1        | 0    | 0        | 0  | 0        | 0  | 0        | 0        | 0    | 0    |

| 7  | 0 | 0 | 0 | 1   | 1        | 8     | 0        | 0    | 0        | 0  | 1        | 0  | 0        | 0        | 0    | 0    |

| 8  | 0 | 0 | 1 | 1   | 1        | FF    | 0        | 0    | 1        | 8  | 0        | 0  | 0        | 0        | 0    | 0    |

| 9  | 1 | 2 | 2 | 1   | 0        | 0     | 1        | 0    | 0        | 0  | 0        | 0  | 0        | 0        | 0    | 0    |

| 10 | 0 | 0 | 0 | 1   | 1        | 8     | 0        | 0    | 0        | 0  | 1        | 0  | 0        | 0        | 0    | 0    |

| 11 | 0 | 2 | 2 | 1   | 0        | 0     | 1        | 0    | 0        | 0  | 0        | 0  | 0        | 0        | 0    | 0    |

| 12 | 2 | 0 | 2 | 1   | 1        | 2     | 0        | 0    | 0        | 0  | 1        | 1  | 0        | 0        | 0    | 0    |

| 13 | 3 | 2 | 0 | 0   | 0        | 0     | 0        | 0    | 0        | 0  | 0        | 0  | 0        | 1        | 0    | 1    |

Part A (5 points) Describe the operation that occurs during cycle 2. Be specific.

## For the remaining parts, assume 0 = 0x44022118 at the end of cycle 2.

Part B (5 points) What is the value of register 0 at the completion of cycle 7 (in hexadecimal).

Part C (5 points) What is the value of register 2 at the completion of cycle 9 (in hexadecimal).

Part D (5 points) What is the value of register 2 at the completion of cycle 12 (in hexadecimal).

Part E (10 points) Describe the operation of this microcode fragment. Be specific.