*Instructions:* This is a closed book, closed note exam. Calculators are not permitted. If you have a question, raise your hand and I will come to you. Please work the exam in pencil and do not separate the pages of the exam. For maximum credit, show your work. *Good Luck!*

Your Name (*please print*)

| 1  | 2  | 3  | 4  | 5  |

|----|----|----|----|----|

|    |    |    |    |    |

|    |    |    |    |    |

| 30 | 32 | 26 | 24 | 23 |

| total |   |

|-------|---|

|       |   |

|       |   |

| 135   | _ |

5 May 2010

5 problems, 6 pages

Final Exam

**Problem 1** (3 parts, 30 points)

### **Instruction Formats, Etc.**

Part A (9 points) Consider the instruction set architecture below with fields containing zeros.

| 000 0000                                         | 00 0000               | 00 0000       | 0 0000 0000 0000 |  |  |  |  |  |

|--------------------------------------------------|-----------------------|---------------|------------------|--|--|--|--|--|

| opcode                                           | dest. reg.            | source 1 reg. | immediate value  |  |  |  |  |  |

|                                                  |                       |               |                  |  |  |  |  |  |

| What is the maxim                                | um number of opcodes? | ?             |                  |  |  |  |  |  |

| What is the number                               | r of registers?       |               |                  |  |  |  |  |  |

| What is the range of the signed immediate value? |                       |               |                  |  |  |  |  |  |

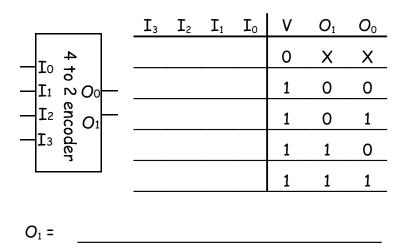

**Part B** (9 points) Suppose the circuit below has the following input priority:  $I_1 > I_3 > I_0 > I_2$ . Complete the truth table by filling in the input values that would produce the given outputs and derive a simplified expression for  $O_1$ .

**Part** C (12 points) For each problem below, compute the operations using the rules of arithmetic, and indicate whether an overflow occurs assuming all numbers are expressed using a **six bit unsigned** and **six bit two's complement** representations.

11010

10001

110101

101101

## Problem 2 (4 parts, 32 points)

**Dueling Designs**

For each part implement the specified device. Label all inputs and outputs.

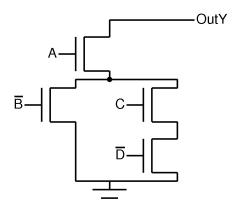

**Part A** (8 points) Complete the incomplete circuit below using N and P type switches and write the expression for  $Out_Y$ .

**Part B** (8 points) Implement the expression in mixed logic notation using NOR gates.

$$OUT_z = \overline{(A + \overline{B + C}) \cdot \overline{D}}$$

**Part** C (8 points) Implement a 2 to 1 MUX using a 1 to 2 decoder and basic gates (AND, OR, NAND, NOR, NOT, & XOR).

**Part D** (8 points) Implement a divide by four counter using toggle cells and minimum additional basic gates.

# **Problem 3** (3 parts, 26 points)

Microcode

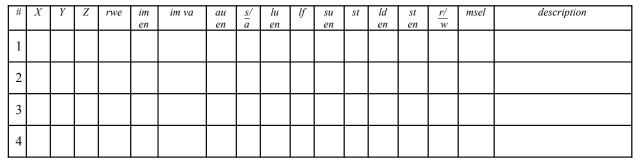

Using the supplied datapath, write microcode fragments to accomplish the following procedures. Express all values, except memory addresses, in hexadecimal notation. Use 'X' when a value is don't cared. For maximum credit, complete the description field. **In each part, modify only registers 7 & 8.**

Part A (5 points)

$$R_7 = (R_8 - 15)/512$$

| # | X | Y | Z | rwe | im<br>en | im va | au<br>en | $\frac{s}{a}$ | lu<br>en | lf | su<br>en | st | ld<br>en | st<br>en | $\frac{r/}{w}$ | msel | description |

|---|---|---|---|-----|----------|-------|----------|---------------|----------|----|----------|----|----------|----------|----------------|------|-------------|

| 1 |   |   |   |     |          |       |          |               |          |    |          |    |          |          |                |      |             |

| 2 |   |   |   |     |          |       |          |               |          |    |          |    |          |          |                |      |             |

| 3 |   |   |   |     |          |       |          |               |          |    |          |    |          |          |                |      |             |

Part B (15 points) Compute mem[4000]  $\oplus$   $R_3$  and store the result in mem[4004].  $\oplus$  means bitwise logical XOR.

| #       | X | Y | Z | rwe | im | im va | au | <u>s/</u> | lu | lf | su | st | ld | st | <u>r/</u> | msel | description |

|---------|---|---|---|-----|----|-------|----|-----------|----|----|----|----|----|----|-----------|------|-------------|

| <u></u> |   |   |   |     | en |       | en | а         | en |    | en |    | en | en | w         |      |             |

| 1       |   |   |   |     |    |       |    |           |    |    |    |    |    |    |           |      |             |

| 2       |   |   |   |     |    |       |    |           |    |    |    |    |    |    |           |      |             |

| -       |   |   |   |     |    |       |    |           |    |    |    |    |    |    |           |      |             |

| 3       |   |   |   |     |    |       |    |           |    |    |    |    |    |    |           |      |             |

| 4       |   |   |   |     |    |       |    |           |    |    |    |    |    |    |           |      |             |

| Ľ       |   |   |   |     |    |       |    |           |    |    |    |    |    |    |           |      |             |

| 5       |   |   |   |     |    |       |    |           |    |    |    |    |    |    |           |      |             |

| 6       |   |   |   |     |    |       |    |           |    |    |    |    |    |    |           |      |             |

Part C (6 points)

$$R_7 = 18 \cdot R_8$$

(multiply R<sub>8</sub> by 18)

5 May 2010

5 problems, 6 pages Final Exam

**Problem 4** (3 parts, 24 points)

Storage

**Part A** (12 points) Consider a **4 Gbit** DRAM chip organized as **64 million addresses** of **64-bit words**. Assume both the DRAM cell and the DRAM chip are square. The column number and offset concatenate to form the memory address. Using the organization approach discussed in class, answer the following questions about the chip. *Express all answers in decimal (not powers of two)*.

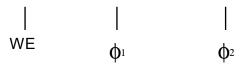

**Part B** (6 points) Implement a register below using *only* latches, pass gates, and inverters (all in icon form). Complete the behavior table at right. Recall that the CLK signal indicates a full  $\Phi_1$   $\Phi_2$  cycle; so the output should be the value at the end of a cycle (for the given inputs).

| <u>In</u> | WE | Clk                   | Out | Out |

|-----------|----|-----------------------|-----|-----|

| Α         | 0  | $\uparrow \downarrow$ |     |     |

| Α         | 1  | $\uparrow\downarrow$  |     |     |

\_\_\_ Out

In \_\_\_

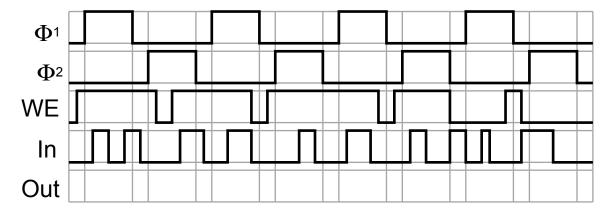

**Part** C (6 points) Assume the following signals are applied to a register with write enable. Draw the output signal **Out**. Draw a vertical line where **In** is sampled. Assume **Out** is initially zero.

5 May 2010

Final Exam

### **Problem 5** (2 parts, 23 points)

### **Assembly Language Programming**

**Part A** (15 points) Write a MIPS subroutine CountX that reads in a vector of integers and counts the number of elements that have the value X (given in register \$1), placing the total count in register \$2. Assume the length of the vector (# of integer elements) is stored in register \$4 and the base address of the vector is in register \$5. The size of the vector may be 0. Follow the steps outlined in the comments in the rightmost column below. You may modify only registers \$2 through \$5.

| label   | instruction | comment                                                                                              |

|---------|-------------|------------------------------------------------------------------------------------------------------|

| CountX: |             | # clear match count (\$2 = 0)                                                                        |

|         |             | <pre># compute end addr: scale vector # length by 4 and add to base address # (2 instructions)</pre> |

| Loop:   |             | <pre># if current elem addr = end address, # then exit loop</pre>                                    |

|         |             | # load current vector elem                                                                           |

|         |             | # if current elem != X then Skip                                                                     |

|         |             | # else increment match count                                                                         |

| Skip:   |             | # inc vector ptr to next elem                                                                        |

|         |             | # loop back                                                                                          |

| Exit:   |             | # return to caller                                                                                   |

Part B (8 points) Consider the following code fragment.

| address | label     | instruction            |

|---------|-----------|------------------------|

| 1000    |           | addi \$10, \$0, 0      |

| 1004    | Loop2:    | lw \$1, (\$12)         |

| 1008    |           | jal CountX             |

| 1012    |           | slt \$9, \$2, \$10     |

| 1016    |           | bne \$9, \$0, Continue |

| 1020    |           | add \$10, \$2, \$0     |

| 1024    | Continue: | addi \$12, \$12, 4     |

| 1028    |           | •••                    |

| 1. | Wha | it is | the | branch | offset | (in ] | bvtes` | ) for | the bne | instruct | ion at | 1016? |

|----|-----|-------|-----|--------|--------|-------|--------|-------|---------|----------|--------|-------|

|----|-----|-------|-----|--------|--------|-------|--------|-------|---------|----------|--------|-------|

If \$10 holds M and \$2 holds the result R of subroutine CountX, what simple mathematical expression do instructions at addresses 1012-1020 compute (express your answer in terms of M and R, not registers)?

| • | T 1 1        | 1013 1030 | 4       |

|---|--------------|-----------|---------|

| • | Instructions | 1017-1070 | compute |

|   |              |           |         |

What is the value of \$31 after the jal instruction at 1008 is executed?

#### 3. The value of \$31 =