| ECE 2030 1:00pm     | Computer Engineering | Spring 2010   |

|---------------------|----------------------|---------------|

| 4 problems, 5 pages | Exam Three           | 21 April 2010 |

*Instructions:* This is a closed book, closed note exam. Calculators are not permitted. If you have a question, raise your hand and I will come to you. Please work the exam in pencil and do not separate the pages of the exam. For maximum credit, show your work. *Good Luck!*

Your Name (*please print*)\_\_\_\_\_

| ECE 2030 1:00pm                                                                | Computer Engineering                                                                                                                                                        | Spring 2010                                                               |

|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| 4 problems, 5 pages                                                            | Exam Three                                                                                                                                                                  | 21 April 2010                                                             |

| Problem 1 (3 parts, 30 point                                                   | ts)                                                                                                                                                                         | Memory Systems                                                            |

| Assume both the DRAM cell a to form the memory address.                        | a <b>1 Gbit</b> DRAM chip organized as <b>12</b><br>and the DRAM chip are square. The co<br>Using the organization approach disc<br>ress all answers in decimal (not power. | olumn number and offset concatenate sussed in class, answer the following |

| total number of bits i                                                         | in address                                                                                                                                                                  |                                                                           |

| number of colum                                                                | mns                                                                                                                                                                         |                                                                           |

| column decoder requir                                                          | red ( <i>n</i> to <i>m</i> )                                                                                                                                                |                                                                           |

| number of words per                                                            | r column                                                                                                                                                                    |                                                                           |

| type of mux required                                                           | d ( <i>n</i> to <i>m</i> )                                                                                                                                                  |                                                                           |

| number of address lines in                                                     | column offset                                                                                                                                                               |                                                                           |

| <b>Part B</b> (10 points) Consider <b>million</b> address by <b>16-bit wor</b> | a memory system with <b>128 million</b> a rd memory DRAM chip.                                                                                                              | addresses of 64-bit words using a 4                                       |

| word address lines for mem                                                     | nory system                                                                                                                                                                 |                                                                           |

| chips needed in one l                                                          | bank                                                                                                                                                                        |                                                                           |

| banks for memory sy                                                            | stem                                                                                                                                                                        |                                                                           |

| memory decoder required                                                        | d ( <i>n</i> to <i>m</i> )                                                                                                                                                  |                                                                           |

| DRAM chips requi                                                               | red                                                                                                                                                                         |                                                                           |

**Part C** (8 points) Design a **128 million address by 4 bit** memory system with **32M x 4** memory chips. *Label all busses and indicate bit width*. Assume R/W is connected and not shown here. Use a bank decoder if necessary. Be sure to include the address bus, data bus, and MSEL.

| ECE 2030 1:00pm     | Computer Engineering | Spring 2010   |

|---------------------|----------------------|---------------|

| 4 problems, 5 pages | Exam Three           | 21 April 2010 |

Problem 2 (3 parts, 26 points)

Datapath Elements

**Part A** (6 points) Suppose the following inputs (in hexadecimal) are applied to the 32-bit barrel shifter used in the datapath. Determine the output (in hexadecimal). Assume the shift amount is drawn from the 16-bit immediate value.

| Shift Type | Shift Amount | Input Value | Output Value |

|------------|--------------|-------------|--------------|

| logical    | 0x0008       | EB25ACE7    |              |

| arithmetic | 0x0010       | BAC19317    |              |

| rotate     | 0xFFF4       | DE2FAB36    |              |

**Part B** (8 points) For each bitwise logical function specification below, determine the LF code (in hexadecimal) to correctly program the logical unit.

| ΧY  | Out             | log | gical function         | LF |

|-----|-----------------|-----|------------------------|----|

| 0 0 | LF <sub>0</sub> |     | $Y + \overline{X}$     |    |

| 1 0 | LF <sub>1</sub> |     | X                      |    |

| 0 1 | LF <sub>2</sub> |     | $X \oplus Y$           |    |

| 1 1 | LF <sub>3</sub> |     | $\overline{X \cdot Y}$ |    |

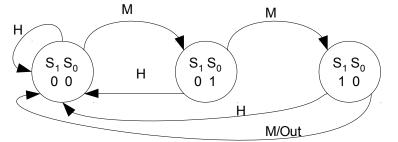

Part C (12 points) Given the following finite state diagram, fill in the state table below.

| <b>S</b> 1 | S0 | H/M | NS <sub>1</sub> | NS <sub>0</sub> | Out | <b>S</b> 1 | S0 | H/M | NS <sub>1</sub> | NS <sub>0</sub> | Out |

|------------|----|-----|-----------------|-----------------|-----|------------|----|-----|-----------------|-----------------|-----|

| 0          | 0  | 0   |                 |                 |     | 1          | 0  | 0   |                 |                 |     |

| 0          | 0  | 1   |                 |                 |     | 1          | 0  | 1   |                 |                 |     |

| 0          | 1  | 0   |                 |                 |     | 1          | 1  | 0   |                 |                 |     |

| 0          | 1  | 1   |                 |                 |     | 1          | 1  | 1   |                 |                 |     |

Give the simplified Boolean expression for computing **Out** in terms of the current state and the input.

Out = \_\_\_\_\_

| ECE 2030 1:00pm     | Computer Engineering | Spring 2010   |

|---------------------|----------------------|---------------|

| 4 problems, 5 pages | Exam Three           | 21 April 2010 |

## Problem 3 (3 parts, 26 points)

Microcode

Using the supplied datapath, write microcode fragments to accomplish the following procedures. Express all values, except memory addresses, in hexadecimal notation. Use 'X' when a value is don't cared. For maximum credit, complete the description field. In each part, modify only registers 7 & 8.

| Pa | rt A | (5 p | poin | ts) |    |       |    | F          | R <sub>7</sub> =( | $R_8^{}-$ | -15)/ | 512 |    |    |           |      |             |

|----|------|------|------|-----|----|-------|----|------------|-------------------|-----------|-------|-----|----|----|-----------|------|-------------|

| #  | X    | Y    | Ζ    | rwe | im | im va | аи | <u>s</u> / | lu                | lf        | su    | st  | ld | st | <u>r/</u> | msel | description |

|    |      |      |      |     | en |       | en | а          | en                |           | en    |     | en | en | W         |      |             |

| 1  |      |      |      |     |    |       |    |            |                   |           |       |     |    |    |           |      |             |

| 2  |      |      |      |     |    |       |    |            |                   |           |       |     |    |    |           |      |             |

| 3  |      |      |      |     |    |       |    |            |                   |           |       |     |    |    |           |      |             |

Part B (15 points) Compute mem[4000]  $\oplus$   $R_3$  and store the result in mem[4004].  $\oplus$  means bitwise logical XOR.

| # | X | Y | Ζ | rwe | im<br>en | im va | au<br>en | $\frac{s}{a}$ | lu<br>en | lf | su<br>en | st | ld<br>en | st<br>en | $\frac{r}{w}$ | msel | description |

|---|---|---|---|-----|----------|-------|----------|---------------|----------|----|----------|----|----------|----------|---------------|------|-------------|

| 1 |   |   |   |     |          |       | en       |               | en       |    | en       |    | en       | en       |               |      |             |

| 2 |   |   |   |     |          |       |          |               |          |    |          |    |          |          |               |      |             |

| 3 |   |   |   |     |          |       |          |               |          |    |          |    |          |          |               |      |             |

| 4 |   |   |   |     |          |       |          |               |          |    |          |    |          |          |               |      |             |

| 5 |   |   |   |     |          |       |          |               |          |    |          |    |          |          |               |      |             |

| 6 |   |   |   |     |          |       |          |               |          |    |          |    |          |          |               |      |             |

| Pa | rt C | (6 p | ooin | ts) |          |       |          | K             | R <sub>7</sub> =1 | $8 \cdot R$ | 8 (      | mul | tiply    | R8 b     | y 18          | )    |             |

|----|------|------|------|-----|----------|-------|----------|---------------|-------------------|-------------|----------|-----|----------|----------|---------------|------|-------------|

| #  | X    | Y    | Ζ    | rwe | im<br>en | im va | au<br>en | $\frac{s}{a}$ | lu<br>en          | lf          | su<br>en | st  | ld<br>en | st<br>en | $\frac{r}{w}$ | msel | description |

|    |      |      |      |     | en       |       | en       | u             | en                |             | en       |     | en       | en       | VV            |      |             |

| 1  |      |      |      |     |          |       |          |               |                   |             |          |     |          |          |               |      |             |

| 2  |      |      |      |     |          |       |          |               |                   |             |          |     |          |          |               |      |             |

|    |      |      |      |     |          |       |          |               |                   |             |          |     |          |          |               |      |             |

| 3  |      |      |      |     |          |       |          |               |                   |             |          |     |          |          |               |      |             |

|    |      |      |      |     |          |       |          |               |                   |             |          |     |          |          |               |      |             |

| 4  |      |      |      |     |          |       |          |               |                   |             |          |     |          |          |               |      |             |

| ECE 2030 1:00pm     | Computer Engineering | Spring 2010   |

|---------------------|----------------------|---------------|

| 4 problems, 5 pages | Exam Three           | 21 April 2010 |

|                     |                      |               |

Problem 4 (2 parts, 18 points)

Part A (8 points) Design a toggle cell using *two transparent latches, two 2 to 1 muxes, and one inverter*. Your toggle cell should have an active high toggle enable input **TE**, and an active low clear input  $\overline{CLR}$ , clock inputs  $\Phi_1$  and  $\Phi_2$ , and an output **Out**. The  $\overline{CLR}$  signal has precedence over **TE**. Label all signals. Also complete the behavior table for the toggle cell.

| TE | $\overline{CLR}$ | CLK                   | Out |

|----|------------------|-----------------------|-----|

| 0  | 0                | $\uparrow \downarrow$ |     |

| 1  | 0                | $\uparrow \downarrow$ |     |

| 0  | 1                | $\uparrow \downarrow$ |     |

| 1  | 1                | ↑↓                    |     |

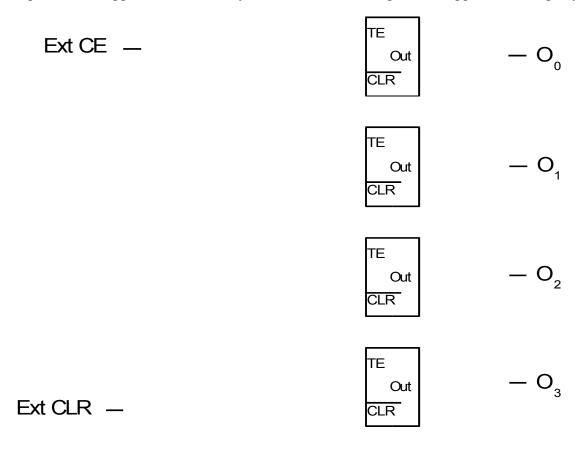

Counters

Part B (10 points) Now combine these toggle cells to build a **divide by eleven** counter. Your counter should have an external clear, external count enable, and four count outputs  $O_3$ ,  $O_2$ ,  $O_1$ ,  $O_0$ . Use any basic gates (AND, OR, NAND, NOR, XOR & NOT) you require. Assume clock inputs to the toggle cells are already connected. Your design must support multi-digit systems.