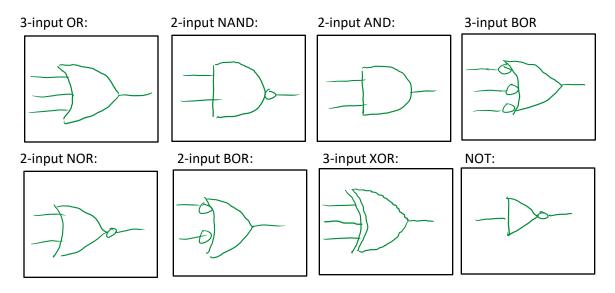

1) Draw the gate schematic symbols for...

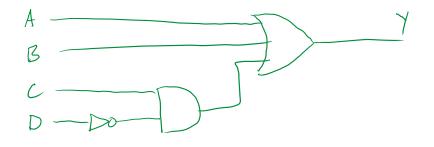

2) Draw a gate-level schematic that implements  $Y = A + B + C \cdot \overline{D}$ . Use a minimal number of gates.

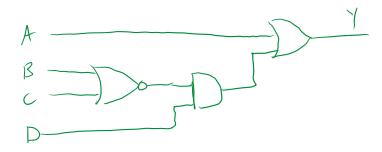

3) Draw a gate-level schematic that implements  $Y = A + \overline{B + C} \cdot D$ . Use a minimal number of gates.

1

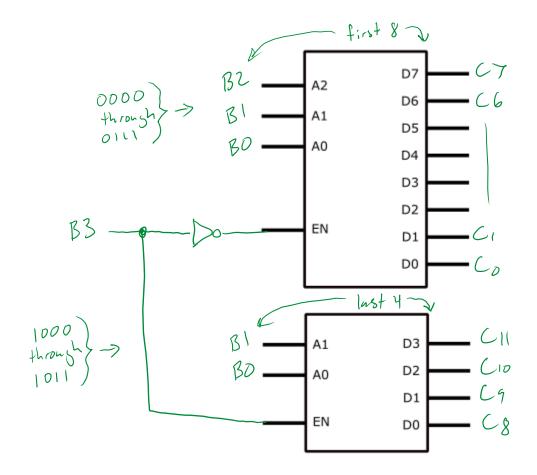

4) You have a three-input OR gate. One input is driven to '1', one input is driven to'0', and one input is not driven. What is the value at the gate's output? forcing 5) You need a 4-to-12 line decoder and you happen to have a 2-to-4 and a 3-to-8 decoder (both with enable inputs). Since four inputs could be decoded to 16 outputs, in this 4-to-12 decoder, inputs "0000" through "1011" will be used, and "1100" (12) through "1111" (15) can be considered "don't cares" and produce any output.

The two decoders are drawn below. Use them to create a 4-to-12 line decoder with inputs B3-0 and outputs C11-0. You can label signals as the needed inputs (B3, B2, B1, B0) or label them with 0 or 1 if they need to be constant. Be sure to label the outputs (C11, C10, [...], C0). You can draw wires as needed, and you can use primitive gates (AND, OR, NOT) if needed. (You do not need very many additional gates. If you start designing a bunch of logic, you're doing something wrong.)

If you were completing the truth table for the following expression:

$$K = \overline{A + B \cdot \overline{C \cdot D}} + (E + F \cdot G)$$

1a) How many rows would the truth table have?

1b) Explain how you can complete half of the truth table by setting one of the inputs to a particular value. Provide the input, the value to make it, and the resulting value for K.

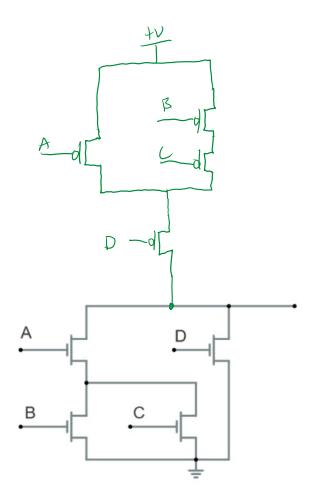

2) Attach an appropriate pull-up network to this pull-down network to create a valid CMOS gate:

3) What is the result if a barrel-shift right by 3 is performed on the following:

1001101

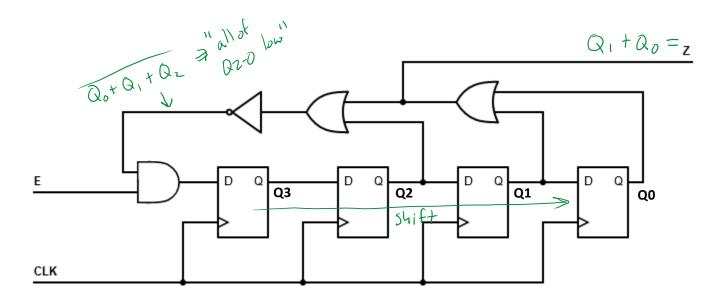

4a) Complete the blank entries in the following transition table based on the state machine above. The state "names" are the same as the state encodings  $Q_3$ - $Q_0$ .

| Current State | Input E | Next State | Output Z |

|---------------|---------|------------|----------|

| 0000          | 1       | 1000       | Ó        |

| 0000          | 0       | 0000       | 0        |

| 1000          | 1       | 1 1 0 0    | 0        |

| 0001          | 1       | 0000       | (        |

| 1101          | 0       | 0110       |          |

| 1001          | 1       | 0 1 0 0    |          |

4b) What is the maximum frequency at which this state machine can be safely clocked? Express your answer as a mathematical expression in terms of the parameters  $T_{pOR}$ ,  $T_{pAND}$ ,  $T_{pNOT}$ ,  $T_{pDFF}$ ,  $T_{SU}$ , and  $T_{H}$ .

(TPOFF + 2TPOR + TPNOT + TPAND + TSN)

4c) After a rising clock edge, how long do you have to wait before the output (Z) is guaranteed to be correct? Express your answer in terms of the same parameters.

TODEE + TOOR

4d) If a rising clock edge occurs at time t=0, during what period of time should input E <u>not</u> change? Express your answer as a range in terms of the timing parameters; e.g.  $-(T_H)$  to  $+(T_H+T_{SU}+T_{PNOT})$ .

- (TSU + TPAND) to + (TH - TPAND)

1) Provide an example of why a "don't care" would exist in the output column of a truth table.

That combo of inputs should never happen, or are outside the specified functionality, or cause something else to happen such that this output doesn't matter.

2) Assuming that the following is a transition table for a Moore state machine, fill in the empty box.

| Q1 | Q0 | Х | Q1+ | Q0+ | Z   |   |

|----|----|---|-----|-----|-----|---|

| 0  | 0  | 0 | 0   | 0   | 0   |   |

| 0  | 0  | 1 | 0   | 1   | 0   |   |

| 0  | 1  | 0 | 1   | 1   | 1   |   |

| 0  | 1  | 1 | 1   | 0   | 1   |   |

| 1  | 0  | 0 | 0   | 0   | 0   |   |

| 1  | 0  | 1 | 0   | 1   | 0   |   |

| 1  | 1  | 0 | 1   | 1   | 1 🗸 | F |

| 1  | 1  | 1 | 0   | 0   | )   |   |

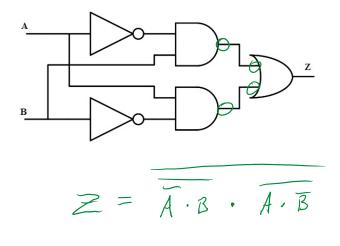

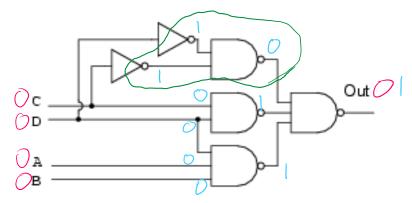

3) Write a Boolean expression that is logically equivalent to the circuit below but that <u>only</u> involves NANDs and inverters. In other words, if I took your expression and directly drew a gate schematic from it, I would only draw NAND gates and inverters.

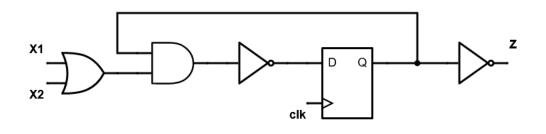

Consider the following circuit:

4a) Does this circuit implement a Mealy or a Moore state machine?

4b) Complete the transition table for the state machine:

Χ1 X2 Q+ Ζ Q () $\bigcirc$  $\mathcal{D}$  $\bigcirc$  $\mathcal{O}$  $\mathcal{O}$  $\mathcal{D}$ () $\mathcal{O}$ () $\bigcirc$  $\mathcal{D}$ 1)  $\mathcal{D}$  $\mathcal{O}$  $\mathcal{O}$ D () $\bigcirc$  next state 1 if current state 0 or both inputs 0.

4c) Using the parameters T<sub>pOR</sub>, T<sub>pAND</sub>, T<sub>pNOT</sub>, T<sub>pDFF</sub>, T<sub>SU</sub>, and T<sub>H</sub>, what is the maximum safe clock frequency for this state machine?

(TPPFF + TPANO + TINOT + TSU)

С В D Υ Α Х Label the rows and columns of the K-map appropriately.  $\left| \right|$ D AB Х DD All prime implicants D  $\mathcal{O}$ Х Eessential D Х Х could be A.D  $\overline{B}$ ·C +  $\overline{B}$ ·D +  $\overline{A}\overline{B}$ 1b) **Y** =

1a) Using the truth table below, create a K-map and solve for a minimal sum-of-products expression.

1c) Regardless of whether or not you circled them or used them in the SoP expression, are there any **non-essential prime implicants** in the K-map above? If so, what are the expressions that represent them?

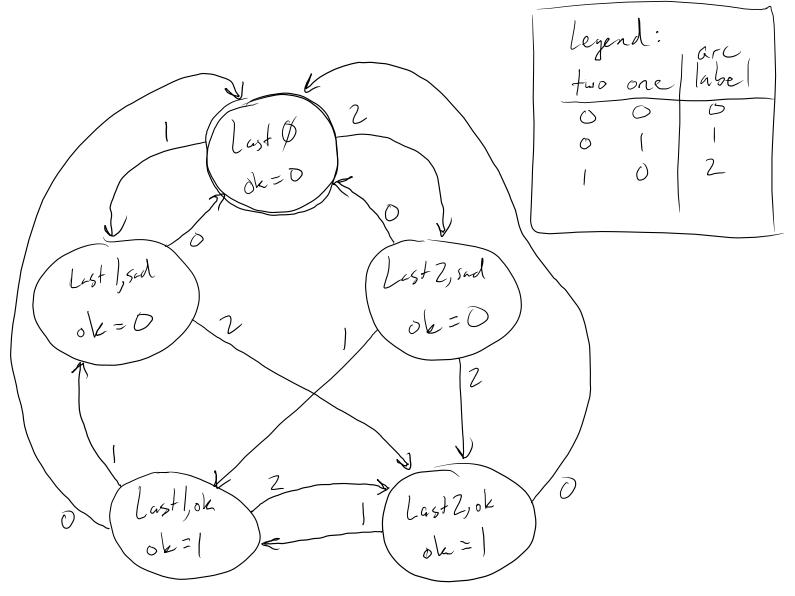

2) Create a state diagram (in the ASM format we used in this class) for a Moore state machine that implements the following behavior. Assume that it is destined to be implemented in digital hardware, so e.g. it has a clock. For all signals, "high", "active" and "1" are synonymous.

The state machine has two inputs, "one" and "two", and one output, "ok". The inputs indicate how many items came out of a machine that clock cycle, which can be none, one, or two (never three).

As long as the sum of items from two cycles (the "current" one and the previous one) is three or more, "ok" should be active. If not enough items are coming out, "ok" should be inactive.

As an example, if input "two" is always active (indicating that two items are coming out each cycle), the output should be active since that's always four items in two cycles. If the inputs oscillate each cycle between "one" being active and "two" being active, the output would be high (since that's always three items in two cycles). If the inputs oscillate each cycle between "one" being active and neither being active, the output would be low (since that's only one item in two cycles).

Assume that at reset, there have not been any items, and thus the output should be inactive.

1) Provide the **decimal value** if these binary numbers are **interpreted as** unsigned, sign-magnitude, 2's complement, and fixed-point numbers in the specified format.

|        | unsigned | sign-magnitude | 2's complement | unsigned fixed-point<br>(NNNN.NN) |

|--------|----------|----------------|----------------|-----------------------------------|

| 010001 | 17       | 17             | 17             | 4.25                              |

| 100111 | 39       | -7             | -25            | 9.75                              |

| 100100 | 36       | -4             | -28            | 9.0                               |

2) Perform the following conversions to hexadecimal.

$$01110010_{2} = \underline{72}_{16}$$

$$101110010_{2} = \underline{172}_{16}$$

$$0000101101110010_{2} = \underline{0872}_{16}$$

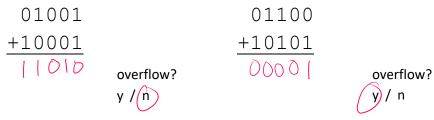

3) Perform the following <u>unsigned</u> operations. Restrict the result to 5 bits, and indicate if overflow occurred.

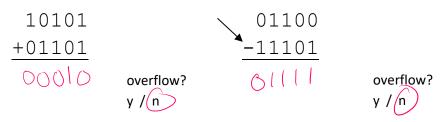

4) Perform the following <u>2's complement</u> operations. Restrict the result to 5 bits, and indicate if overflow occurred.

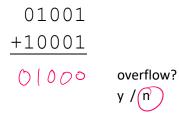

5) Perform the following <u>sign-magnitude</u> operation. Restrict the result to 5 bits, and indicate if overflow occurred.

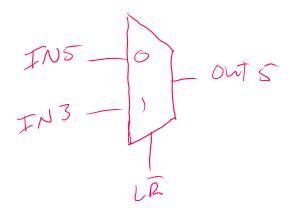

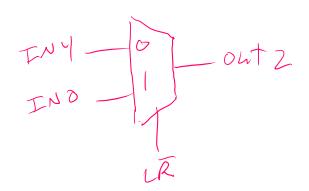

6) Assume that there is a 6-signal bus named IN<sub>5-0</sub>. You need to create logic for OUT<sub>5-0</sub>, where OUT is the result of arithmetically-shifting IN by two places. However, whether the shift is left or right is selected by another signal,  $L/\overline{R}$ .

For this problem, you <u>only need to create logic for  $OUT_5$  and  $OUT_2$ </u>.

To summarize, you have access to signals  $IN_{5-0}$  and  $L/\overline{R}$  and you need to create logic for  $OUT_5$  and  $OUT_2$  as specified above. You can use primitive gates and any of [encoders, decoders, multiplexers, demultiplexers] if desired.

LR OUTS OUTZ O INS INY I INS INO

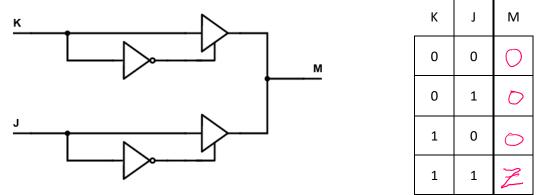

1) Complete the truth table for this circuit.

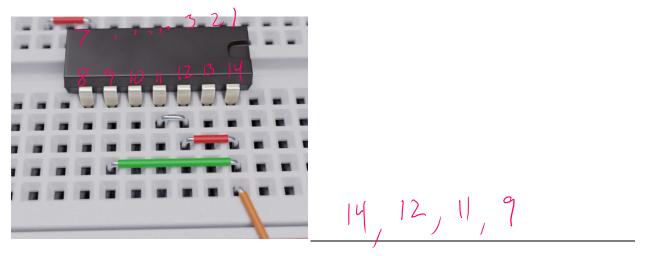

2) In the following image, assume that the wire going off the bottom connects to Vcc. Which pins on the chip are connected to Vcc? Provide the pin <u>numbers</u> as you would find them in the chip's datasheet.

3) The following table is from a chip's datasheet. Ignore the strobe signal. What logic device does this chip contain?

|               | Select<br>Inputs |   | Data Inputs Strobe |    |     | Strobe | Output |     |

|---------------|------------------|---|--------------------|----|-----|--------|--------|-----|

|               | В                | Α | C0                 | C1 | C2  | C3     | G      | Y   |

|               | Х                | Х | X                  | Х  | X   | Х      | н      | L   |

| $\sim$        | L                | L | 1/15               | Х  | X   | X      | L      | L   |

| $\mathcal{O}$ | L                | L |                    | Х  | Х   | Х      | L      | н   |

| ,             | L                | н | X                  | L  | Х   | X      | L      | J L |

|               | L                | н | X                  | н  | Х   | Х      | L      | н   |

| 2             | н                | L | X                  | X  |     | X      | L      | s L |

| V             | Н                | L | X                  | Х  | ∖н∫ | Х      | L      | н   |

| $\gamma$      | н                | н | x                  | Х  | X   |        | L      | L L |

| )             | Н                | н | x                  | х  | x   | Н      | L      | н   |

## **Function Table**

5) This is table is from the datasheet from the type of flip-flop that you used in the second lab. If you can't cause any clock edges, how can you force the Q output to be high?

| FUNCTION TABLE |     |              |   |                |                    |  |  |  |

|----------------|-----|--------------|---|----------------|--------------------|--|--|--|

|                | INP | OUTPUT       |   |                |                    |  |  |  |

| PRE            | CLR | CLK          | D | Q              | Q                  |  |  |  |

| L              | н   | / x          | Х | H              | L                  |  |  |  |

| H              |     | Х            | Х | 5              | Н                  |  |  |  |

| L              | L)  | Х            | Х | (н†)           | H†                 |  |  |  |

| H              | H   |              | Н | <u>H</u>       | L                  |  |  |  |

| н              | Н   | $\mathbf{A}$ | L | L              | Н                  |  |  |  |

| Н              | Н   | L            | Х | Q <sub>0</sub> | $\overline{Q}_{0}$ |  |  |  |

<sup>+</sup> This configuration is nonstable; that is, it does not persist when PRE or CLR returns to its inactive (high) level.

Mala pre low, preterably ctr high.

6) Assume you have built a circuit implementing the following logic and are currently testing it.

Known in pink Expected in blue

You drive the inputs all low, and your test equipment (e.g. a myDAQ) indicates that the output is low. You do some debugging and determine that the problem must be in the circuit somewhere (i.e. it's not the myDAQ, connections to the myDAQ, power supply, etc.) so you start testing nodes in the circuit. Which node in the circuit is a good node to probe first, and why?

The output of the top NAND or either output of the NOTS, because any of those being wrong could be directly responsible for the incorrect output.