## Problem 1 (32 points)

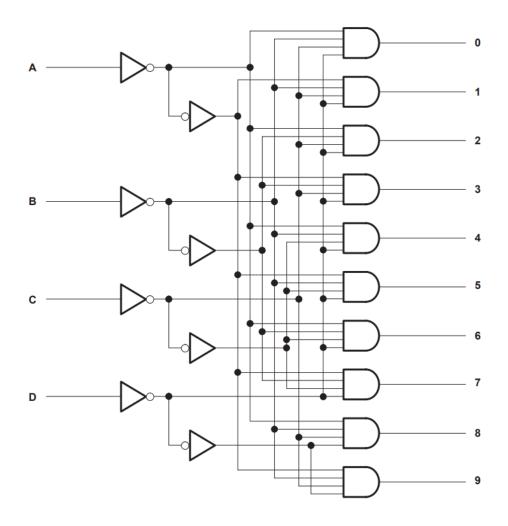

Below is a (slightly modified) excerpt from a 74HC42 chip – a 4-to-10 line decoder. Although 4-to-16 is more traditional, 10 is a common number, and this fits nicely into a standard 16-pin chip (4 inputs + 10 outputs + power + ground).

a) If the inputs (A, B, C, and D) are interpreted as a binary number, which one would be considered the least-significant (as related to the output numbering)?

b) Which output(s) will be high if all of the inputs are high?

c) If the propagation delay through an inverter is 8 ns and the propagation delay through a 4-input AND gate is 24 ns, what is the worst-case delay from any input to any output? In other words, if you change all of the inputs, how long do you have to wait before all of the outputs are correct?

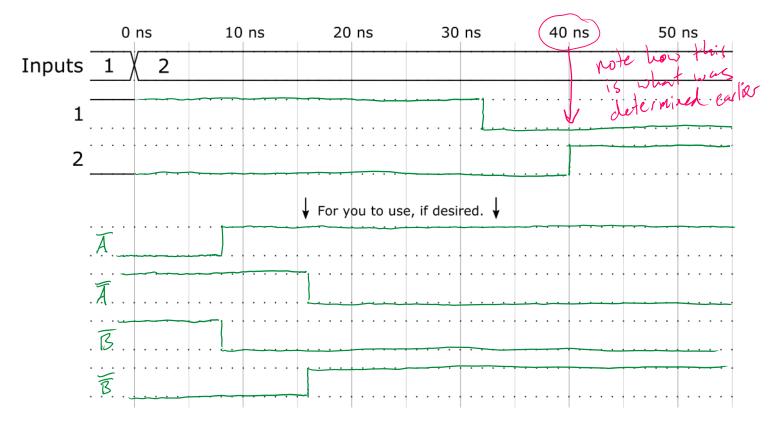

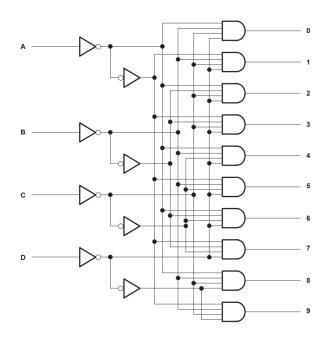

d) Complete the following timing diagram for outputs 1 and 2 after the inputs switch from "1" to "2"; in other words, the inputs change from "0001" to "0010" at t = 0 ns. Output 1 is currently high, and eventually output 2 should be high. Extra space is provided at the bottom in case you want to sketch additional signals, and an extra copy of the schematic is below for your reference. Use the 8 ns and 24 ns delays from above.

## Problem 2 (25 points)

Provide the decimal equivalent if these binary numbers are interpreted as unsigned, sign-magnitude, 2's complement, and fixed-point numbers in the specified format.

|      | unsigned | sign-magnitude | 2's complement | unsigned fixed-point (NN.NN) |  |  |

|------|----------|----------------|----------------|------------------------------|--|--|

| 0100 | Ч        | U              | Ц              | 1                            |  |  |

| 1011 | 11       | -3             | -5             | 2.75                         |  |  |

| 1100 | 12       | -4             | _ \            | 3                            |  |  |

Perform the following conversions to hexadecimal.

$$1010_2 = A_{16}$$

$$11010_2 = IA$$

$$0000111101011010_2 = 0F SA_{16}$$

Perform the following unsigned operations. Restrict the result to 5 bits, and indicate if overflow occurred.

Perform the following 2's complement operations. Restrict the result to 5 bits, and indicate if overflow occurred.

Perform the following sign-magnitude operation. Restrict the result to 5 bits, and indicate if overflow occurred.

## Problem 3 (24 points)

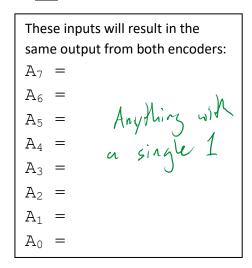

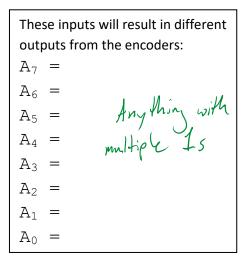

a) Consider two 8-to-3 priority encoders, each with inputs A<sub>7-0</sub> and outputs E<sub>2-0</sub>, but with opposite priority: in one, A<sub>7</sub> has the highest priority and A<sub>0</sub> has the lowest, and in the other, A<sub>0</sub> is highest and A<sub>7</sub> is lowest.

Provide a set of input values (<u>1s and 0s</u>) that would result in the *same* output from both encoders, and one that would result in *different* outputs from each encoder. There are <u>many</u> correct answers here; you only need to provide one for each case.

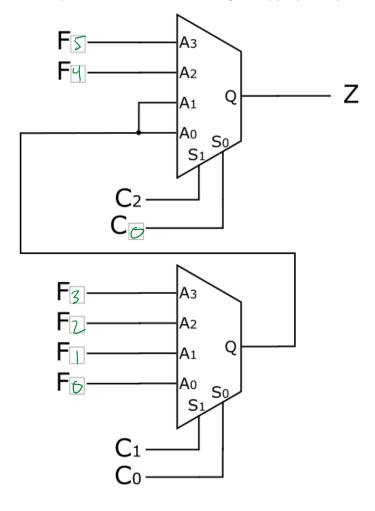

b) The goal of the circuit below is to multiplex six signals (F<sub>5</sub>-F<sub>0</sub>) onto signal Z based on the three control signals C<sub>2</sub>-C<sub>0</sub>. Complete the design by filling in the grey boxes. You need to choose the one remaining control signal, and you need to number the F signals appropriately (so that they make sense based on the control signals).

## Problem 4 (18 points)

Fill in the result of the specified shifts.

|                             | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 |

|-----------------------------|---|---|---|---|---|---|---|---|

| Logical shift right by 2    | 0 | O | 1 | D | ) | 1 | 0 | 1 |

| ·                           |   |   |   |   |   |   |   |   |

|                             | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 |

| Logical shift left by 2     | ) | ) | 0 | 1 | 0 |   | 0 | 0 |

| ·                           |   |   |   |   |   |   |   |   |

|                             | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 |

| Arithmetic shift right by 2 | 1 | ) | ( | 0 | 1 | ) | 0 | 1 |

|                             |   |   |   |   |   |   |   |   |

|                             | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 |

| Arithmetic shift left by 2  | ) | 1 | O | 1 | 0 | 1 | 0 | 0 |

| ·                           |   |   |   |   |   |   |   |   |

|                             | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 |

| Barrel shift left by 2      | 1 | 1 | D | 1 | 0 | ) | 1 | 0 |

| ·                           |   |   |   |   |   |   |   |   |

|                             | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 |

| Barrel shift right by 2     | 0 | 1 | 1 | 0 | l | 1 | 0 |   |