#### ECE2020 A Fall 2018 Final Exam

- Only a writing implement and five pages of notes (front and back) may be used on this exam (no electronics).

- If the meaning of any question is not clear, please ask for clarification.

- Partial credit can only be awarded for work shown.

## Honor pledge:

On my honor, I pledge that I will neither receive nor provide improper assistance in the completion of this test. I understand and accept my responsibility as a member of the Georgia Tech Community to uphold the Honor Code at all times, and I know that I have options for reporting honor violations at osi.gatech.edu.

| GTID: Signature: |  |

|------------------|--|

|------------------|--|

#### **Boolean Identities**

**FOIL**

Disappearing opposite

| Identity          | A + 0 = A                                            | $A \cdot 1 = A$                                   |

|-------------------|------------------------------------------------------|---------------------------------------------------|

| Dominance         | A + 1 = 1                                            | $A\cdot 0=0$                                      |

| Idempotence       | A + A = A                                            | $A \cdot A = A$                                   |

| Inverse           | $A + \overline{A} = 1$                               | $A\cdot\overline{A}=0$                            |

| Commutative       | A + B = B + A                                        | $A \cdot B = B \cdot A$                           |

| Associative       | A + (B + C) = (A + B) + C                            | $A \cdot (B \cdot C) = (A \cdot B) \cdot C$       |

| Distributive      | $A \cdot (B+C) = A \cdot B + A \cdot C$              | $A + B \cdot C = (A + B) \cdot (A + C)$           |

| Absorption        | $A\cdot (A+B)=A$                                     | $A + A \cdot B = A$                               |

| DeMorgan's        | $\overline{(A+B)} = \overline{A} \cdot \overline{B}$ | $\overline{(A\cdot B)}=\overline{A}+\overline{B}$ |

| Double Complement | $\bar{\bar{A}} = A$                                  |                                                   |

$(A+B)\cdot (C+D) = A\cdot C + A\cdot D + B\cdot C + B\cdot D$

$A + \overline{A} \cdot B = A + B$

| Decimal | Binary | Hex |

|---------|--------|-----|

| 0       | 0      | 0   |

| 1       | 1      | 1   |

| 2       | 10     | 2   |

| 3       | 11     | 3   |

| 4       | 100    | 4   |

| 5       | 101    | 5   |

| 6       | 110    | 6   |

| 7       | 111    | 7   |

| 8       | 1000   | 8   |

| 9       | 1001   | 9   |

| 10      | 1010   | А   |

| 11      | 1011   | В   |

| 12      | 1100   | С   |

| 13      | 1101   | D   |

| 14      | 1110   | E   |

| 15      | 1111   | F   |

| 2-6 | 0.015625 |

|-----|----------|

| 2-5 | 0.03125  |

| 2-4 | 0.0625   |

| 2-3 | 0.125    |

| 2-2 | 0.25     |

| 2-1 | 0.5      |

| 20  | 1        |

| 21  | 2        |

| 22  | 4        |

| 23  | 8        |

| 24  | 16       |

| 25  | 32       |

| 26  | 64       |

| 27  | 128      |

| 28  | 256      |

| 29  | 512      |

| 210 | 1024     |

# 3-to-8 Line Decoder with Enable

| A2 | A1 | Α0 | EN | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----|----|----|----|----|----|----|----|

| 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  |

| 0  | 0  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  |

| 0  | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  |

| 0  | 1  | 1  | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  |

| 1  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  |

| 1  | 0  | 1  | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  |

| 1  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  |

| 1  | 1  | 1  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| Χ  | Χ  | Χ  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

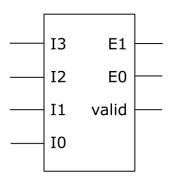

# 8-to-3 Priority Encoder (Priority A7->A0)

| Α7 | A6 | A5 | Α4 | А3 | A2 | A1 | Α0 | E2 | E1 | E0 | V |

|----|----|----|----|----|----|----|----|----|----|----|---|

| 1  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | 1  | 1  | 1  | 1 |

| 0  | 1  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | 1  | 1  | 0  | 1 |

| 0  | 0  | 1  | Χ  | Χ  | Χ  | Χ  | Χ  | 1  | 0  | 1  | 1 |

| 0  | 0  | 0  | 1  | Χ  | Χ  | Χ  | Χ  | 1  | 0  | 0  | 1 |

| 0  | 0  | 0  | 0  | 1  | Х  | Χ  | Χ  | 0  | 1  | 1  | 1 |

| 0  | 0  | 0  | 0  | 0  | 1  | Χ  | Χ  | 0  | 1  | 0  | 1 |

| 0  | 0  | 0  | 0  | 0  | 0  | 1  | Χ  | 0  | 0  | 1  | 1 |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 1 |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 |

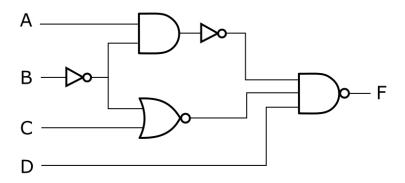

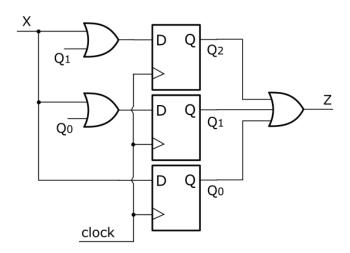

Write a Boolean expression for the circuit above. Do not simplify it (e.g. through algebraic manipulation).

Complete the truth table for the circuit above.

| Α | В | С | D | F |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 |   |

| 0 | 0 | 0 | 1 |   |

| 0 | 0 | 1 | 0 |   |

| 0 | 0 | 1 | 1 |   |

| 0 | 1 | 0 | 0 |   |

| 0 | 1 | 0 | 1 |   |

| 0 | 1 | 1 | 0 |   |

| 0 | 1 | 1 | 1 |   |

| 1 | 0 | 0 | 0 |   |

| 1 | 0 | 0 | 1 |   |

| 1 | 0 | 1 | 0 |   |

| 1 | 0 | 1 | 1 |   |

| 1 | 1 | 0 | 0 |   |

| 1 | 1 | 0 | 1 |   |

| 1 | 1 | 1 | 0 |   |

| 1 | 1 | 1 | 1 |   |

(Just putting this in a box to use the empty space over here. It's a separate question, unrelated to anything else on this page.)

Write a Boolean expression that implements the following logic. If input "cat" is 1, the output should be 1 no matter what, otherwise the output should be the opposite of input "dog".

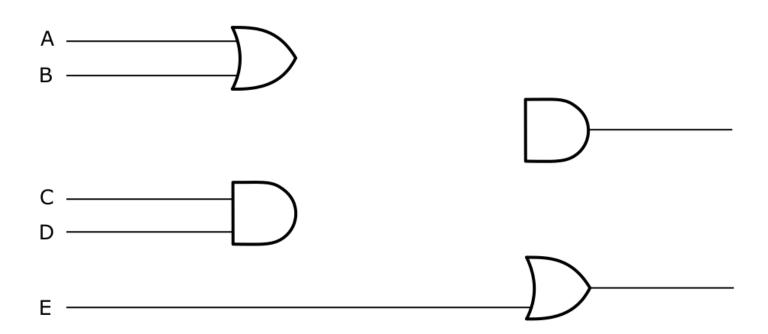

<u>Draw a mixed-logic diagram</u> that produces the two logic expressions below. Re-use the repeated term  $C \cdot D$ . A starting point has been provided to make grading easier, so you only need to fill in the middle connections. Once drawn, convert the diagram to be implemented <u>using only NAND gates</u> (and inverters). Minimize the number of inverters.

$$X = \overline{\overline{A} + B} \cdot C \cdot D$$

$$Y = \overline{C \cdot D} + E$$

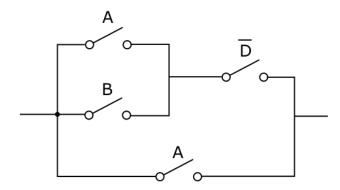

Write a Boolean expression that represents the connection between the sides of the switch network above. Do not simplify the expression (e.g. through algebraic manipulation).

Now simplify the above expression as much as possible using algebraic manipulation.

Draw a new switch network that directly implements the simplified expression derived above.

Circle the minimum number of prime implicants of 1s on the K-map below to cover the function.

|                            | $\overline{C}\overline{D}$ | $\overline{C}D$ | C D | C D |

|----------------------------|----------------------------|-----------------|-----|-----|

| $\overline{A}\overline{B}$ | 0                          | 1               | 1   | 0   |

| $\overline{A} B$           | 1                          | 0               | 0   | 1   |

| A B                        | 1                          | 1               | 1   | 1   |

| $A\overline{B}$            | 1                          | 0               | 1   | 1   |

Write the sum-of-products expression corresponding to the implicants you circled on the K-map above.

Are there any prime implicants in the K-map above (regardless of whether you circled them or not) that are not essential? If so, what are the Boolean expressions for them?

How many maxterms are in the K-map above?

No longer specifically referring to the K-map above, but to some other K-map of four inputs A, B, C, and D, give an example of an implicant (in Boolean expression form) that covers a single minterm.

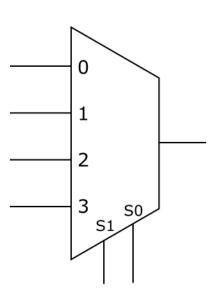

You've been asked to create a circuit that implements the following behavior, where input signals "fwd" and "rev" select an appropriate output for "dir", which is sometimes based on another input "go". To make the design easier, you've been asked to use a multiplexer. Design a circuit around the multiplexer by adding signal labels (which can include the named signals and '1' and '0') and primitive gates (AND, OR, NOT, etc.).

| fwd | rev | dir |

|-----|-----|-----|

| 0   | 0   | 0   |

| 0   | 1   | go  |

| 1   | 0   | go  |

| 1   | 1   | 0   |

You know that the 4-to-2 encoder above uses priority of either  $I_3>I_2>I_1>I_0$  or  $I_0>I_1>I_2>I_3$ . Describe the simplest way to test the device to determine which priority it uses.

Regardless of the priority, what set of inputs will ensure that all three outputs are active?

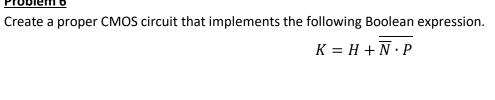

Create a CMOS-like circuit (NFETs in a pull-down network and PFETs in a pull-up network) that tri-states output R when input S is low and connects Vdd and GND (a bad thing to do) when input S is high.

What is the following (base-10) value represented in unsigned binary? Use as many digits as necessary.

$$2^{12}-1 =$$

Convert the following base-10 numbers to 8-bit signed 2's complement representations.

Convert this 8-bit 2's complement number to 12 bits.

## 11011000 ->

Convert the following base-10 number to an 8-bit sign-magnitude representation.

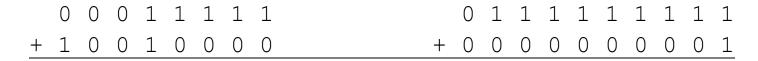

Perform these unsigned binary additions.

Interpret the following as 2's complement numbers. Keeping the same number of bits, will the additions result in correct or incorrect answers?

correct / incorrect

correct / incorrect

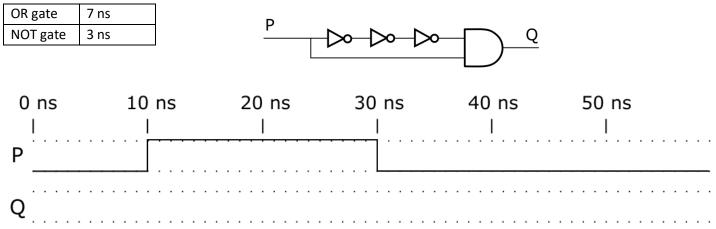

Sketch a timing diagram for this circuit's response to the provided input. Use the provided propagation delays.

In the state machine above, after a rising edge on the clock, what is the soonest that the output Z might change? Express your answer in terms of parameters of the circuit elements; e.g. propagation delay of a 2-input OR gate T<sub>pOR2</sub>.

In the circuit above, assume that nothing has happened for a long time, and then X changes at time t=0. To ensure correct <u>state machine behavior</u> (i.e. not only correct flip-flop behavior but also functional behavior of the state machine), when is the soonest that the <u>first</u> rising clock edge can occur?

Continuing from the above problem, what is the soonest that the second rising clock edge can occur?

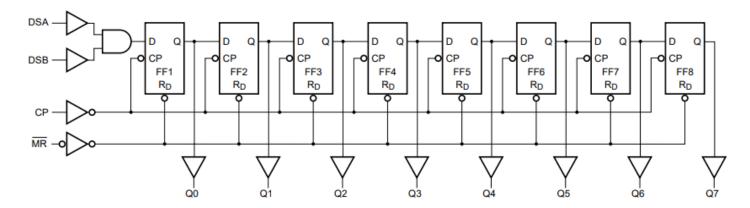

This is the internal diagram of a 74HC164 chip, which is a shift register. Signal "MR" is "master reset", and the function of the rest of the signals you should be able to determine from the diagram.

Is this a seral-to-parallel or parallel-to-serial shift register? Briefly describe how you came to that conclusion.

The device has two signals DSA and DSB. If you only need one of those for a system you're designing, what should you do with the other?

If the outputs, as numbered, were used as a binary number  $Q_{7-0}$ , would data be shifted into this device most-significant or least-significant bit first?

Create a state diagram for a state machine that implements the behavior described here.

The state machine monitors two buttons that produce signals, named A and B, that are 1 when the button is pressed and 0 when the button is not pressed. The state machine controls one output, named T.

When one button is pressed (not both), the output should toggle (i.e. switch from 0 to 1 or 1 to 0). Even if the button is held down, the output should only toggle once.

If both buttons are pressed, the output should toggle every clock cycle.

When no buttons are pressed, the output should turn off as soon as possible.