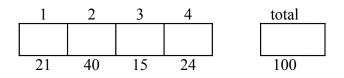

| ECE 2030C 2:00 p.m.  | Computer Engineering | Fall 2010       |

|----------------------|----------------------|-----------------|

| _4 problems, 6 pages | Exam Two             | 27 October 2010 |

|                      |                      |                 |

*Instructions:* This is a closed book, closed note exam. Calculators are not permitted. If you have a question, raise your hand and I will come to you. Please work the exam in pencil and do not separate the pages of the exam. For maximum credit, show your work. *Good Luck!*

Your Name (*please print*)

| ECE 2030C 2:00 p.m. | Computer Engineering | Fall 2010       |

|---------------------|----------------------|-----------------|

| 4 problems, 6 pages | Exam Two             | 27 October 2010 |

Problem 1 (3 parts, 21 points)

State

Part A (8 points) Implement a transparent latch using only inverters and pass gates. Label the inputs In and En, and output Out.

Part B (7 points) Consider a register with a selectable *write enable* (WE) and *read enable* (RE). It is implemented with transparent latches, a 2 to 1 mux, and a pass gate. Describe its behavior by completing the output values. Also indicate when a write and/or a read is being performed.

|       |                        | _    | IN | WE | RE | CLK                   | OUT | write? | read? |

|-------|------------------------|------|----|----|----|-----------------------|-----|--------|-------|

| IN —  |                        |      | А  | 0  | 0  | $\uparrow \downarrow$ |     |        |       |

| WE —  | Register               | - RE | А  | 1  | 0  | ↑↓                    |     |        |       |

| ··- ( | $\phi_1 \qquad \phi_2$ | J    | А  | 0  | 1  | $\uparrow \downarrow$ |     |        |       |

|       |                        | -    | А  | 1  | 1  | ↑↓                    |     |        |       |

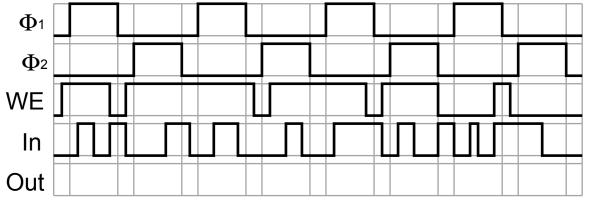

Part C (6 points) Assume the following signals are applied to a register with write enable Draw the output signal **Out**. Draw a vertical line where **In** is sampled. *Draw crosshatch where* **Out** *is unknown*.

2 \_\_\_\_\_

Problem 2 (4 parts, 40 points)

Number Representations & Arithmetic

Part A (10 points) Convert the following notations:

| decimal notation | <br>binary notation  |

|------------------|----------------------|

| 327              |                      |

|                  | 100101.1001          |

| 44.125           |                      |

| octal notation   | hexadecimal notation |

| 73.37            |                      |

|                  | 0x5A.D               |

Part B (12 points) For these 12 bit representations, determine the most positive value and the step size (difference between sequential values). All answers should be expressed in decimal notation. Fractions (e.g., 3/16ths) may be used. All signed representations are two's complement.

| representation                             | most positive value | step size |

|--------------------------------------------|---------------------|-----------|

| unsigned integer<br>(12 bits) . (0 bits)   |                     |           |

| signed fixed-point<br>(6 bits) . (6 bits)  |                     |           |

| unsigned fixed-point<br>(8 bits). (4 bits) |                     |           |

| signed fixed-point<br>(10 bits) . (2 bits) |                     |           |

Part C (6 points) A 29 bit floating point representation has a 17 bit mantissa field, a 11 bit exponent field, and one sign bit.

| What is the largest value that can be represented (closest to infinity)? | 2 |

|--------------------------------------------------------------------------|---|

|--------------------------------------------------------------------------|---|

What is the smallest value that can be represented (closest to zero)?

How many decimal significant figures are supported?

Part D (12 points) For each problem below, compute the operations using the rules of arithmetic, and indicate whether an overflow occurs assuming all numbers are expressed using a **six bit unsigned fixed-point** and **six bit two's complement fixed-point** representations.

|                 | 1010.<br>+ 111.  |           |           | 0.11  | - •       | 01.01<br>00.10 |             | )1.11<br>)0.01 |

|-----------------|------------------|-----------|-----------|-------|-----------|----------------|-------------|----------------|

| result          | <u> </u>         | <u>11</u> | <u> </u>  | 10.00 | - 11      | 00.10          | <u>- 1(</u> | <u>JU.U1</u>   |

| unsigned error? | $\Box$ no $\Box$ | yes       | □ no      | □ yes | □ no      | □ yes          | □ no        | □ yes          |

| signed error?   | $\Box$ no $\Box$ | yes       | $\Box$ no | □ yes | $\Box$ no | □ yes          | $\Box$ no   | □ yes          |

| ECE 2030C 2:00 p.m. | Computer Engineering | Fall 2010       |

|---------------------|----------------------|-----------------|

| 4 problems, 6 pages | Exam Two             | 27 October 2010 |

Problem 3 (2 parts, 15 points)

**Building Blocks**

Part A (7 points) Complete the following truth table for a priority encoder. Assume the priority order (from highest to lowest) is  $I_2 > I_0 > I_3 > I_1$

|                                                                                              | Io | $I_1$ | $I_2$ | $I_3$ | V | <i>O</i> <sub>1</sub> | <i>O</i> <sub>0</sub> |

|----------------------------------------------------------------------------------------------|----|-------|-------|-------|---|-----------------------|-----------------------|

| 4                                                                                            |    |       |       |       | 0 | Х                     | Х                     |

| $-I_1 \sim O_0$                                                                              |    |       |       |       | 1 | 0                     | 0                     |

|                                                                                              |    |       |       |       | 1 | 0                     | 1                     |

| $ \begin{array}{c} -I_{0} \\ +I_{0} \\ -I_{1} \\ -I_{2} \\ -I_{2} \\ -I_{3} \\ \end{array} $ |    |       |       |       | 1 | 1                     | 0                     |

|                                                                                              |    |       | -     |       | 1 | 1                     | 1                     |

Part B (8 points) Implement a 2 to 1 multiplexer using only basic gates (AND, OR, NAND, NOR, NOT). Label all inputs and outputs.

| ECE 2030C 2:00 p.m. | Computer Engineering | Fall 2010       |

|---------------------|----------------------|-----------------|

| 4 problems, 6 pages | Exam Two             | 27 October 2010 |

|                     |                      |                 |

Problem 4 (3 parts, 24 points)

Counters

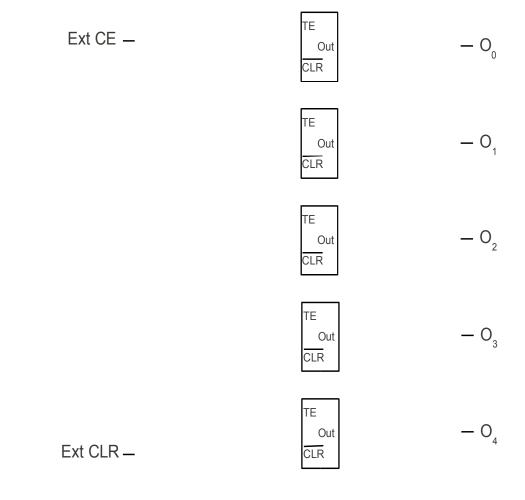

Part A (7 points) Implement a toggle cell using *only transparent latches and basic gates (XOR, AND, OR, NAND, NOR, NOT)*. Use an icon for the transparent latches. Label the inputs TE,  $\overline{CLR}$ ,  $\Phi_1$ ,  $\Phi_2$  and the output **Out**.

Part B (8 points) Now combine these toggle cells to build a **divide by 24** counter. Your counter should have an external clear, external count enable, and five count outputs  $O_4$ ,  $O_3$ ,  $O_2$ ,  $O_1$ ,  $O_0$ . Use any basic gates (AND, OR, NAND, NOR, & NOT) you require. Assume clock inputs to the toggle cells are already connected. *Your design should support multi-digit systems*.

| ECE 2030C 2:00 p.m. | Computer Engineering | Fall 2010       |

|---------------------|----------------------|-----------------|

| 4 problems, 6 pages | Exam Two             | 27 October 2010 |

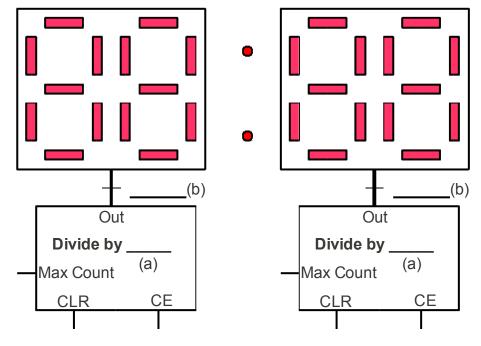

Part C (9 points) Build a military timer (HH:MM) which displays hours (0...23) on the left and minutes (0...59) on the right as follows. In the diagram below:

a) Fill in the label "Divide by \_\_\_\_" on each counter.

b) Label the number of output wires coming from each counter to its attached display.

c) Draw the appropriate wiring connections to allow this military timer to correctly respond to external clear (Ext CLR) and count enable (Ext CE) signals, and to correctly increment the hour count when the maximum number of minutes have passed while the clock is still running.

Use any basic gates you require. Assume clock inputs are already connected.

| Ext CLR | Ext CE |

|---------|--------|